Professional Documents

Culture Documents

Unit 3

Unit 3

Uploaded by

PradhibaSelvaraniOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Unit 3

Unit 3

Uploaded by

PradhibaSelvaraniCopyright:

Available Formats

The Processor

Introduction

CPU performance factors

Instruction count

Determined by ISA and compiler

CPI and Cycle time

Determined by CPU hardware

We will examine two MIPS implementations

A simplified version

A more realistic pipelined version

Simple subset, shows most aspects

Memory reference: lw, sw

Arithmetic/logical: add, sub, and, or, slt

Control transfer: beq, j

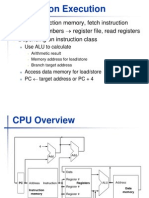

Instruction Execution

PC instruction memory, fetch instruction

Register numbers register file, read registers

Depending on instruction class

Use ALU to calculate

Arithmetic result

Memory address for load/store

Branch target address

Access data memory for load/store

PC target address or PC + 4

CPU Overview

Multiplexers

Cant just join

wires together

Use multiplexers

Control

Logic Design Basics

Information encoded in binary

Low voltage = 0, High voltage = 1

One wire per bit

Multi-bit data encoded on multi-wire buses

Combinational element

Operate on data

Output is a function of input

State (sequential) elements

Store information

Combinational Elements

AND-gate

Y = A & B

A

B

Y

I0

I1

Y

M

u

x

S

Multiplexer

Y = S ? I1 : I0

A

B

Y

+

A

B

Y

ALU

F

Adder

Y = A + B

Arithmetic/Logic Unit

Y = F(A, B)

Sequential Elements

Register: stores data in a circuit

Uses a clock signal to determine when to

update the stored value

Edge-triggered: update when Clk changes

from 0 to 1

D

Clk

Q

Clk

D

Q

Sequential Elements

Register with write control

Only updates on clock edge when write

control input is 1

Used when stored value is required later

D

Clk

Q

Write

Write

D

Q

Clk

Clocking Methodology

Combinational logic transforms data during

clock cycles

Between clock edges

Input from state elements, output to state

element

Longest delay determines clock period

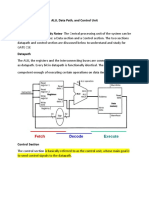

Building a Datapath

Datapath

Elements that process data and addresses

in the CPU

Registers, ALUs, muxs, memories,

We will build a MIPS datapath

incrementally

Refining the overview design

Instruction Fetch

32-bit

register

Increment by

4 for next

instruction

R-Format Instructions

Read two register operands

Perform arithmetic/logical operation

Write register result

Load/Store Instructions

Read register operands

Calculate address using 16-bit offset

Use ALU, but sign-extend offset

Load: Read memory and update register

Store: Write register value to memory

Branch Instructions

Read register operands

Compare operands

Use ALU, subtract and check Zero output

Calculate target address

Sign-extend displacement

Shift left 2 places (word displacement)

Add to PC + 4

Already calculated by instruction fetch

Branch Instructions

Just

re-routes

wires

Sign-bit wire

replicated

Composing the Elements

First-cut data path does an instruction in

one clock cycle

Each datapath element can only do one

function at a time

Hence, we need separate instruction and data

memories

Use multiplexers where alternate data

sources are used for different instructions

R-Type/Load/Store Datapath

Full Datapath

You might also like

- Implementation of A 16-Bit RISC Processor Using FPGA ProgrammingDocument25 pagesImplementation of A 16-Bit RISC Processor Using FPGA ProgrammingTejashree100% (3)

- Chapter 04 Computer Organization and Design, Fifth Edition: The Hardware/Software Interface (The Morgan Kaufmann Series in Computer Architecture and Design) 5th EditionDocument137 pagesChapter 04 Computer Organization and Design, Fifth Edition: The Hardware/Software Interface (The Morgan Kaufmann Series in Computer Architecture and Design) 5th EditionPriyanka Meena67% (6)

- Computer Organization and Design Pipeliing-Chapter+4 SlidesDocument131 pagesComputer Organization and Design Pipeliing-Chapter+4 SlidesVishlesh PatelNo ratings yet

- Method Statement For Demolation and Installation of Chain Link Fencing & Boundery Wall For Site Temporary Facilites ClientDocument8 pagesMethod Statement For Demolation and Installation of Chain Link Fencing & Boundery Wall For Site Temporary Facilites ClienteshwarNo ratings yet

- Instagram Creators Handbook - IGTV PDFDocument48 pagesInstagram Creators Handbook - IGTV PDFAndrei Neațu100% (1)

- Vesys Test Drive READMEDocument29 pagesVesys Test Drive READMEHota bNo ratings yet

- The ProcessorDocument27 pagesThe ProcessorPradhibaSelvaraniNo ratings yet

- CO Unit 2Document125 pagesCO Unit 2KarthikNo ratings yet

- CA U3 Sjit PDFDocument95 pagesCA U3 Sjit PDFThe Smart Boy KungFuPawnNo ratings yet

- The Processor: The Hardware/Software Interface 5Document149 pagesThe Processor: The Hardware/Software Interface 5ayylmao kekNo ratings yet

- Chap 4 1Document57 pagesChap 4 1Tin TranNo ratings yet

- Chapter 4 The ProcessorDocument131 pagesChapter 4 The ProcessorAk GptNo ratings yet

- The Processor: (Datapath and Pipelining)Document144 pagesThe Processor: (Datapath and Pipelining)paranoid486No ratings yet

- Single Cycle Datapath PDFDocument30 pagesSingle Cycle Datapath PDFShivam KhandelwalNo ratings yet

- Multi Cycle Data PathDocument21 pagesMulti Cycle Data PathSushma S MurthyNo ratings yet

- Chapter 4 The ProcessorDocument131 pagesChapter 4 The ProcessorRahman AsmadNo ratings yet

- Chapter 04 RISC VDocument130 pagesChapter 04 RISC VTrí ĐôNo ratings yet

- Lecture 12Document29 pagesLecture 12Neal SchneierNo ratings yet

- Patterson6e MIPS Ch04 PPTDocument137 pagesPatterson6e MIPS Ch04 PPTalapabainviNo ratings yet

- Chapter 04Document131 pagesChapter 04deepaknittrichyNo ratings yet

- CSA Seoultech 04Document137 pagesCSA Seoultech 04이다원No ratings yet

- Chapter - 04 Mips Assembly Data PathDocument137 pagesChapter - 04 Mips Assembly Data PathAbubakar sabirNo ratings yet

- Chapter 04 Computer Architecture and DDocument95 pagesChapter 04 Computer Architecture and DPooja VashisthNo ratings yet

- Comp206 Lecture7Document44 pagesComp206 Lecture7huseyinefekaragozNo ratings yet

- Chapter 5: The Processor: Datapath and Control: I. MIPS ImplementationDocument6 pagesChapter 5: The Processor: Datapath and Control: I. MIPS ImplementationNguyễn Quốc VũNo ratings yet

- Processor PDFDocument98 pagesProcessor PDFArafat KhanNo ratings yet

- Computer Architecture: Chapter 4: The Processor Part 1Document51 pagesComputer Architecture: Chapter 4: The Processor Part 1Kiet LuongNo ratings yet

- The ProcessorDocument83 pagesThe Processortinni09112003No ratings yet

- COA 2013 Chapter 4 The ProcessorDocument153 pagesCOA 2013 Chapter 4 The Processornazakiamartine04No ratings yet

- Unit 3Document55 pagesUnit 3ladukhushi09No ratings yet

- Computer Architecture MIPS Processor DescriptionDocument41 pagesComputer Architecture MIPS Processor DescriptionAsif HussainNo ratings yet

- Cyan 2800398239029h09fn0ivj0vcjb0Document16 pagesCyan 2800398239029h09fn0ivj0vcjb0Anonymous zWBss8LKNo ratings yet

- CENG 331 Course Slides Chapter 5Document73 pagesCENG 331 Course Slides Chapter 5Odunayo KusoroNo ratings yet

- The Processor - IntroductionDocument10 pagesThe Processor - Introductionsas21-d01-s6-cs15No ratings yet

- MIPS Datapath IF DecoderDocument14 pagesMIPS Datapath IF DecoderMartin Fuentes AcostaNo ratings yet

- Final-Assignment CoverDocument12 pagesFinal-Assignment CoverHứa Đăng KhoaNo ratings yet

- Su L17 Processor DatapathDocument33 pagesSu L17 Processor DatapathindramanokaranNo ratings yet

- Lesson 2 ALU and Data Path Study NotesDocument5 pagesLesson 2 ALU and Data Path Study NotesRustin FariolenNo ratings yet

- An Introduction To INTEL 8085 Microprocessor: By:Ravindra Nadh.V, Assistant Professor, GST, BangaloreDocument35 pagesAn Introduction To INTEL 8085 Microprocessor: By:Ravindra Nadh.V, Assistant Professor, GST, BangaloreVasudev Rao KonjetiNo ratings yet

- Lecture # 7Document20 pagesLecture # 7Aafaaq AmirNo ratings yet

- Cs2253 - Computer Architecture 16 Marks Question Bank With Hints Unit - I 1. Explain Basic Functional Units of Computer. Input UnitDocument18 pagesCs2253 - Computer Architecture 16 Marks Question Bank With Hints Unit - I 1. Explain Basic Functional Units of Computer. Input UnitArun VijayNo ratings yet

- Coa HW2Document6 pagesCoa HW2Mohammed AyadNo ratings yet

- 6 Mips DatapathDocument55 pages6 Mips Datapath1352 : NEEBESH PADHYNo ratings yet

- CS3352 DPCO UNIT 4 NOTES EduEnggDocument67 pagesCS3352 DPCO UNIT 4 NOTES EduEnggBadri NarayananNo ratings yet

- DPCO Unit-4Document44 pagesDPCO Unit-4john wickNo ratings yet

- Co Unit2 Part1Document11 pagesCo Unit2 Part1Manjushree N.SNo ratings yet

- CO Unit 1-2Document14 pagesCO Unit 1-2Aravinder Reddy SuramNo ratings yet

- 8086 Architecture and Addressing ModesDocument53 pages8086 Architecture and Addressing ModeskarthiNo ratings yet

- LogicDocument36 pagesLogicSwanNo ratings yet

- Ca06 2014 PDFDocument53 pagesCa06 2014 PDFPance CvetkovskiNo ratings yet

- 2.1 8085 PROGRAMMING 2.1.1 Addressing Modes (Ref2: Section 0.9.2)Document16 pages2.1 8085 PROGRAMMING 2.1.1 Addressing Modes (Ref2: Section 0.9.2)UiNo ratings yet

- Input Unit: Five Basic Components of Computer SystemDocument9 pagesInput Unit: Five Basic Components of Computer SystemJefin PaulNo ratings yet

- 8085 MicroprocessorDocument20 pages8085 Microprocessorjeravi84No ratings yet

- Basic Computer OrganizationDocument23 pagesBasic Computer OrganizationKibrom HaftuNo ratings yet

- Svcet: 1. What Is MIPS, MIPS Instruction, MIPS ImplementationDocument24 pagesSvcet: 1. What Is MIPS, MIPS Instruction, MIPS ImplementationSamia MumuNo ratings yet

- Ch01 Basic Concepts and Computer EvolutionDocument36 pagesCh01 Basic Concepts and Computer EvolutionMark ShanNo ratings yet

- DSP Processors: We Have Seen That The Multiply and Accumulate (MAC) Operation Is Very Prevalent in DSP ComputationDocument9 pagesDSP Processors: We Have Seen That The Multiply and Accumulate (MAC) Operation Is Very Prevalent in DSP ComputationertwertNo ratings yet

- Computer Organization-Single CycleDocument23 pagesComputer Organization-Single Cyclev2brotherNo ratings yet

- Computer Organization and ArchitectureDocument108 pagesComputer Organization and ArchitectureMuhammad Zeeshan MughalNo ratings yet

- CO Assignment-1: ISA With Reference To MIPSDocument3 pagesCO Assignment-1: ISA With Reference To MIPSMANAS AGARWALNo ratings yet

- CST202 - Question BankDocument64 pagesCST202 - Question Banksona sasikumarNo ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- CS6212 Programming and Data Structures Laboratory IDocument1 pageCS6212 Programming and Data Structures Laboratory IPradhibaSelvaraniNo ratings yet

- Blooming All The Way!!!: Cognitive Level Assessment QuestionsDocument2 pagesBlooming All The Way!!!: Cognitive Level Assessment QuestionsPradhibaSelvaraniNo ratings yet

- The ProcessorDocument27 pagesThe ProcessorPradhibaSelvaraniNo ratings yet

- Flynns ClassificationDocument27 pagesFlynns ClassificationPradhibaSelvaraniNo ratings yet

- Kamaraj College of Engineering and Technology Department of CseDocument3 pagesKamaraj College of Engineering and Technology Department of CsePradhibaSelvaraniNo ratings yet

- Lesson Plan (Theory) : Kamaraj College of Engineering and TechnologyDocument2 pagesLesson Plan (Theory) : Kamaraj College of Engineering and TechnologyPradhibaSelvaraniNo ratings yet

- Smriti Swar - Brij - Sharma Interim ReportDocument96 pagesSmriti Swar - Brij - Sharma Interim Reportsms0331No ratings yet

- Modification Instruction: Truck, Medium, Mc2 - Unimog - All TypesDocument7 pagesModification Instruction: Truck, Medium, Mc2 - Unimog - All TypesmichaelNo ratings yet

- College of Forestry and Natural Resources Field of Study/Specialized Courses Prerequisite (S) Units Offering Production & Industrial ForestryDocument1 pageCollege of Forestry and Natural Resources Field of Study/Specialized Courses Prerequisite (S) Units Offering Production & Industrial ForestryAnai GelacioNo ratings yet

- ASSINGMENT Pavement EngineeringDocument12 pagesASSINGMENT Pavement Engineeringmrafiruler90No ratings yet

- I LuxDocument24 pagesI LuxNirav M. BhavsarNo ratings yet

- American Option PricingDocument12 pagesAmerican Option PricingsatyaNo ratings yet

- Using MySQL With LabVIEWDocument49 pagesUsing MySQL With LabVIEWsion2010363650% (2)

- OJT ReportDocument52 pagesOJT ReportMARK MATUMBA0% (1)

- Pwwha: Delhi 10RDocument44 pagesPwwha: Delhi 10Rserrano.flia.coNo ratings yet

- 2010-2016: Formation and Pre-Debut Activities: The X FactorDocument1 page2010-2016: Formation and Pre-Debut Activities: The X FactorHQNo ratings yet

- Laboratory Exercise 1Document23 pagesLaboratory Exercise 1Paterson SoroñoNo ratings yet

- Accenture AptitudeDocument122 pagesAccenture AptitudeHarshith P.BNo ratings yet

- Garden Growers Nursery Technician: Job DescriptionDocument2 pagesGarden Growers Nursery Technician: Job DescriptionKevin PittNo ratings yet

- Mechanics L5 PDFDocument52 pagesMechanics L5 PDFCharlie LaiNo ratings yet

- The Sine and Cosine Rule QuestionsDocument20 pagesThe Sine and Cosine Rule QuestionsJacob WilliamNo ratings yet

- Literature Review Empirical ResearchDocument4 pagesLiterature Review Empirical Researchaflssjrda100% (1)

- FB125Document29 pagesFB125Hoangvinh DuongNo ratings yet

- Roles & Responsibilities of DSMDocument24 pagesRoles & Responsibilities of DSMkurutalaNo ratings yet

- Catálogo de Bombas de Diafragma - ARODocument52 pagesCatálogo de Bombas de Diafragma - AROIvan RodrigoNo ratings yet

- Student'S Profile Sheet: Personal BackgroundDocument4 pagesStudent'S Profile Sheet: Personal BackgroundValerie Amor SalabaoNo ratings yet

- Alcatel-Lucent Omniswitch 6360: Stackable Gigabit Ethernet Lan Switch FamilyDocument9 pagesAlcatel-Lucent Omniswitch 6360: Stackable Gigabit Ethernet Lan Switch FamilyredNo ratings yet

- Bike Booking System FinalDocument29 pagesBike Booking System FinalThe WatcherNo ratings yet

- Project Proposal TemplateDocument2 pagesProject Proposal TemplatejorifeberdenuevoespinosaNo ratings yet

- Soil ReportDocument9 pagesSoil ReportHabib Ur RahmanNo ratings yet

- Raymond Murphy-English Grammar in Use With Answers and CD ROM - A Self-Study Reference and Practice Book For Intermediate Students of English-Cambridge University Press (2004)Document13 pagesRaymond Murphy-English Grammar in Use With Answers and CD ROM - A Self-Study Reference and Practice Book For Intermediate Students of English-Cambridge University Press (2004)Thiago Dos Reis100% (1)

- Artificial Intelligence & It's Applications in Banking SectorDocument61 pagesArtificial Intelligence & It's Applications in Banking SectorClassic PrintersNo ratings yet

- GOLDEN TERRY ProfileDocument15 pagesGOLDEN TERRY ProfileMuru GanNo ratings yet