Professional Documents

Culture Documents

300 Alrudainy 48 Slides Modify1

300 Alrudainy 48 Slides Modify1

Uploaded by

Haider AlrudainyOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

300 Alrudainy 48 Slides Modify1

300 Alrudainy 48 Slides Modify1

Uploaded by

Haider AlrudainyCopyright:

Available Formats

A Scalable Physical Model for Nano-Electro

Mechanical Relays

Haider M. Alrudainy ,

1 Dr. Andrey Mokhov ,

2 Prof. Alex Yakovlev 3

School of Electrical and Electronic Engineering, Newcastle University, Newcastle Upon Tyne, GB

1h.m.a.alrudainy@ncl.ac.uk,2andrey.mokhov@ncl.ac.uk,3alex.yakovlev@ncl.ac.uk

Motivation Proposed Model:

g g g

Design of scalable and accurate physical model

Cgc

R ch/2 R ch/2 R ch/2 R ch/2 Cgs + Cgd

that can be plugged into the standard EDA

R ch/2 R ch/2

software. f

Ccb Cgb Cgb

Overcome the simulation convergence problems, Cgs

R pox R pox Cgd Cgs

R pox + R con

R pox + R con Cgd Cgb

due to numerous number of non-linear parasitic + R con + R con R pox + R pox + R con

R trace R trace R con

capacitance and contact discontinuities. d d b s

a b s d s

j b

(Ccg +Ccb ) ≪ Cgb , (Ccg +Ccb ) ≪ Cgd , (Ccg +Ccb ) ≪ Cgs (Ccg +Ccb ) could be ignored. g

Needed Switch simulator: 𝑅𝑡𝑟𝑎𝑐𝑒 ≪ 𝑅𝑝𝑜𝑥 , 𝑅𝑡𝑟𝑎𝑐𝑒 ≪ 𝑅𝑐𝑜𝑛 , 𝑅𝑡𝑟𝑎𝑐𝑒 ≪ 𝑅𝑐ℎൗ2 𝑅𝑡𝑟𝑎𝑐𝑒 could be ignored. Cgs + Cgd

High accuracy. Linearize the parasitic capacitors (Cgd , Cgs ) added them together.

Cgb

Fast execution time. Linearized the parasitic resistor (𝑅𝑐𝑜𝑛 ) then added to 𝑅𝑐ℎൗ2 and 𝑅𝑝𝑜𝑥 .

R pox + R con +

R pox + R con +

d R ch/2

Tackling the convergence problems. b R ch/2

s

Is highly in demand ….. Results:

4.6 % latency error rate between the standard and Model execution time versus clock speed and number of stages.

proposed model

Suspended Gate Relay: Increase to less than 7% After cascading of 40 Simulator needs long time to approach the solution at low

AND Gate in series switching frequency.

A2

A1

A0

A1 A10 A40

A0 Simulation Time [n sec.]

A1 A10 A40

Spring-Mass-Damper

Linear Fit

7

K b Model

Measured Error

Error (Latency) [%]

6.5

Gate: 𝐏 + 𝐩𝐨𝐥𝐲 − 𝐒𝐢𝟎.𝟒 𝐆𝐞𝟎.𝟔

6

𝐂𝐠𝐜

Channel Channel

5.5

𝐑 𝐜𝐡/𝟐 𝐂𝐠𝐛 𝐑 𝐜𝐡/𝟐

𝐂𝐠𝐬 𝐂𝐜𝐛 𝐑 𝐩𝐨𝐱 + 𝐑 𝐜𝐨𝐧 𝐂𝐠𝐝

5

𝐑 𝐩𝐨𝐱 + 𝐑 𝐜𝐨𝐧

Base Drain

4 4.5

Insulator : 𝐀𝐥𝟐 𝐎𝟑

Substrate : Si

0 5 10 15 20 25 30 35 40

Fig. 1: NEM Relay Structure Based on [1] Number of stages

Number of stages

Table below shows the evaluation of the proposed model in terms of latency, scalability, and simulation time.

Methodology:

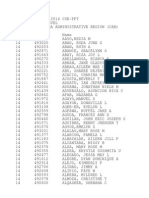

Lumped Verilog-A model based NEMS No. of Latency Simulation Time

Mechanical dynamics: spring, damper, mass Circuits Relays Std. Pro. Error(%) Std. Pro. Improvement

Electrical parasitic: capacitor and resistor (%)

Source AND 2 15ns 15.7ns 4.6 3m 4s 2m 23s 23

𝐕𝐒𝐨𝐮𝐫𝐜𝐞 𝟎

𝐅𝐞𝐥𝐞 𝟎 Logic OR 2 15ns 15.6ns 4.0 4m 49s 3m 26s 29

𝐅𝐯𝐝𝐰 𝟎 XOR 2 15ns 15.5ns 3.3 848 ms 783 ms 7

Body

D-Latch 4 15ns 15.7ns 4.6 1m 47s 1m 2s 41

𝒁ሷ

𝒁ሶ

𝐙𝟎

2-input C- 10 15ns 16ns 6.0 6m 28s 3m 55s 39

= −𝒌 − 𝒌𝒎

Lumped electrical parameters4

Sequential element

Lumped mechanical parameters

𝐕𝐒𝐨𝐮𝐫𝐜𝐞 𝟏

𝒎

𝐅𝐞𝐥𝐞 𝟏 3-input C- 14 Div. 17ns ---- Div. 9m 19s ----

Suspended-Gate NEM Relay

𝐅𝐯𝐝𝐰 𝟏 element

𝑸𝒎

1-bit CSA 22 15ns 17ns 13 13m 23s 9m 37s 28

𝟏

𝐙𝟏 1-bit CRA

Verilog-A

Verilog-A

𝒁

𝒁

Arithmetic 12 15ns 16ns 6.0 6m 52s 4m 37s 33

𝟐

𝟏

2-bit CRA 24 Div. 18ns ---- Div. 14m 34s ----

Gate

+

5-bit CRA 60 Div. 22ns ---- Div. 31m 35s ----

𝒎

𝟎

𝟏

5.9 28

𝑭

Average

𝒆𝒍𝒆. + 𝑭𝒗𝒅𝒘

Conclusion: References:

[1]M. Spencer, F. Chen, et al., "Demonstration of integrated micro-

𝐕𝐒𝐨𝐮𝐫𝐜𝐞

𝐅𝐞𝐥𝐞 𝐍 electro-mechanical relay circuits for VLSI applications," IEEE

Journal of Solid-State Circuits, vol. 46, pp. 308-320, // 2011.

𝐅𝐯𝐝𝐰 𝐍 The new proposed NEM model can be used for simulation a large scale

𝐍

[2] F. K. Chowdhury, D. Saab, and M. Tabib-Azar, "Single-device

design with less than 6 % error rate. "XOR" and "AND" gates for high speed, very low power LSI

𝐅 𝐜𝐨𝐧𝐭𝐚𝐜𝐭

𝐙𝐍 mechanical processors," Sensors and Actuators, A: Physical, // 2012.

The proposed model can be integrated in the existing EDAs and can be

utilised for better scalability and less execution time than the standard

model.

Contact Contact Follow Publicati

Mechanical Electrica The methodology of simulating the suspended gate NEM Relay could be us on

adopted to simulate the NEMS in [2].

Drain

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5834)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1093)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (852)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (903)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (541)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (349)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (824)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (405)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Financial Analysis of - Toys "R" Us, Inc.Document30 pagesFinancial Analysis of - Toys "R" Us, Inc.Arabi AsadNo ratings yet

- SMC V Gomez Case Digest Krystal Grace PaduraDocument2 pagesSMC V Gomez Case Digest Krystal Grace PaduraKrystal Grace D. PaduraNo ratings yet

- Patient Privacy ActionDocument4 pagesPatient Privacy Actionjessica writes2021No ratings yet

- 57984c89bf389 (BPI CAP) Account Opening Form and Client Agreement 04-06-2016Document15 pages57984c89bf389 (BPI CAP) Account Opening Form and Client Agreement 04-06-2016Nancy Hernandez- TurlaNo ratings yet

- Technical Engineering College - Department of Electrical Power EngineeringDocument3 pagesTechnical Engineering College - Department of Electrical Power EngineeringHaider AlrudainyNo ratings yet

- Advance Microprocessor and MicrocontrollerDocument2 pagesAdvance Microprocessor and MicrocontrollerHaider AlrudainyNo ratings yet

- PLC Maintenance and Troubleshooting - Module 1: - Intro To PLC'sDocument57 pagesPLC Maintenance and Troubleshooting - Module 1: - Intro To PLC'sHaider Alrudainy100% (1)

- Untitled 2Document10 pagesUntitled 2Haider AlrudainyNo ratings yet

- Balancing Regularity and Burstiness in New Computer Systems: Async 2014 ConferenceDocument16 pagesBalancing Regularity and Burstiness in New Computer Systems: Async 2014 ConferenceHaider AlrudainyNo ratings yet

- DFT - Slides Power ElectronicDocument14 pagesDFT - Slides Power ElectronicHaider AlrudainyNo ratings yet

- Emf1 SyllabusDocument2 pagesEmf1 SyllabusHaider AlrudainyNo ratings yet

- New Microsoft Word FGHFGHFGDocument2 pagesNew Microsoft Word FGHFGHFGHaider AlrudainyNo ratings yet

- 2014 ISLPED Smart ButterflyDocument4 pages2014 ISLPED Smart ButterflyHaider AlrudainyNo ratings yet

- Basic Fpga Arch XilinxDocument39 pagesBasic Fpga Arch XilinxAli AhmadNo ratings yet

- Process: Add Menu Item Master, Definition, Price: Step ActionDocument7 pagesProcess: Add Menu Item Master, Definition, Price: Step ActionPrince HakimNo ratings yet

- DURA-BASE Mats (Newpark) Pics Well Pads Roads Containment 1998-2013 APR2...Document35 pagesDURA-BASE Mats (Newpark) Pics Well Pads Roads Containment 1998-2013 APR2...JAVIER ANDRADE MARTINEZNo ratings yet

- SRM Admin 6 5 PDFDocument188 pagesSRM Admin 6 5 PDFMuhammad Majid KhanNo ratings yet

- Samier AC 2017 Islamic Public Administration Tradition Historical TheoreticalDocument19 pagesSamier AC 2017 Islamic Public Administration Tradition Historical TheoreticalJunaid AliNo ratings yet

- Infinity Lithium INF Research Update 1702373977Document17 pagesInfinity Lithium INF Research Update 1702373977Israel Gómez SánchezNo ratings yet

- PSG Presentation PDFDocument19 pagesPSG Presentation PDFAjayvidyanand SharmaNo ratings yet

- Configuring Apache HTTP Server and Tomcat With Mod JKDocument3 pagesConfiguring Apache HTTP Server and Tomcat With Mod JKPravin UttarwarNo ratings yet

- 757 TowbarDocument20 pages757 TowbarNad RockNo ratings yet

- The Future of Presentations Exploring AI Slideshow MakerDocument5 pagesThe Future of Presentations Exploring AI Slideshow Makerai-slideshow-makerNo ratings yet

- The Cow Theory of EconomicsDocument2 pagesThe Cow Theory of EconomicsRajesk WostiNo ratings yet

- Party Wise Sales DetailsDocument7 pagesParty Wise Sales DetailsDeepak ChandraNo ratings yet

- PHM and Value AdditionDocument3 pagesPHM and Value AdditionNikhil GourNo ratings yet

- 2014-03-12 New York Progress and Protection PAC - Declaration of Clyde WilcoxDocument51 pages2014-03-12 New York Progress and Protection PAC - Declaration of Clyde WilcoxConnaissableNo ratings yet

- Acquisition and Disposition of Property, Plant and EquipmentDocument63 pagesAcquisition and Disposition of Property, Plant and EquipmentKashif Raheem100% (1)

- Mihalis KAVARATZISDocument18 pagesMihalis KAVARATZISPaulo FerreiraNo ratings yet

- Distribution, Abundance and Population Status of Four Indigenous Threatened Tree Species in The Arba Minch Natural Forest, Southern EthiopiaDocument9 pagesDistribution, Abundance and Population Status of Four Indigenous Threatened Tree Species in The Arba Minch Natural Forest, Southern EthiopiaMihretu AbrhamNo ratings yet

- Investment AgreementDocument37 pagesInvestment AgreementPandurr100% (6)

- TLE - AFA - FISH - PROCESSING 7 - 8 - w3Document4 pagesTLE - AFA - FISH - PROCESSING 7 - 8 - w3Marilyn Lamigo Bristol100% (1)

- CSE-PPT CAR Prof PDFDocument21 pagesCSE-PPT CAR Prof PDFPhilNewsXYZNo ratings yet

- Consent To Rescission RevisedDocument1 pageConsent To Rescission RevisedpaulNo ratings yet

- Oil and Natural Gas Corporation Ltd. Vasai East Development ProjectDocument7 pagesOil and Natural Gas Corporation Ltd. Vasai East Development Projectmathew1965No ratings yet

- Banking and The Management of Financial InstitutionsDocument60 pagesBanking and The Management of Financial InstitutionsMinh TiếnNo ratings yet

- The Industry's First Diaphragm Integrity Monitor: Models NTA, TTA, FXTDocument2 pagesThe Industry's First Diaphragm Integrity Monitor: Models NTA, TTA, FXTCarlos A. MurilloNo ratings yet

- Paul Pignataro Leveraged BuyoutsDocument11 pagesPaul Pignataro Leveraged Buyoutspriyanshu14No ratings yet

- Design Standards Report - FinalDocument35 pagesDesign Standards Report - FinalaberraNo ratings yet

- Standard RSA Dock LevellersDocument29 pagesStandard RSA Dock LevellersEl-Kim NyooNo ratings yet