Professional Documents

Culture Documents

Half-Adder:: One-Bit Binary Numbers

Half-Adder:: One-Bit Binary Numbers

Uploaded by

Kiran Abbas0 ratings0% found this document useful (0 votes)

29 views6 pagesA half-adder is a combinational circuit that adds two one-bit binary numbers and outputs their sum and carry. However, it cannot be used for multi-digit addition because it can only add two bits, not a bit plus a carry. A full adder can add three bits at a time - the two input bits plus a carry bit. When adding multi-digit binary numbers, half adders are only used for the least significant bit while full adders are used for all other bits to account for potential carries from the previous stage.

Original Description:

Original Title

Half-Adder.ppt

Copyright

© © All Rights Reserved

Available Formats

PPT, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentA half-adder is a combinational circuit that adds two one-bit binary numbers and outputs their sum and carry. However, it cannot be used for multi-digit addition because it can only add two bits, not a bit plus a carry. A full adder can add three bits at a time - the two input bits plus a carry bit. When adding multi-digit binary numbers, half adders are only used for the least significant bit while full adders are used for all other bits to account for potential carries from the previous stage.

Copyright:

© All Rights Reserved

Available Formats

Download as PPT, PDF, TXT or read online from Scribd

Download as ppt, pdf, or txt

0 ratings0% found this document useful (0 votes)

29 views6 pagesHalf-Adder:: One-Bit Binary Numbers

Half-Adder:: One-Bit Binary Numbers

Uploaded by

Kiran AbbasA half-adder is a combinational circuit that adds two one-bit binary numbers and outputs their sum and carry. However, it cannot be used for multi-digit addition because it can only add two bits, not a bit plus a carry. A full adder can add three bits at a time - the two input bits plus a carry bit. When adding multi-digit binary numbers, half adders are only used for the least significant bit while full adders are used for all other bits to account for potential carries from the previous stage.

Copyright:

© All Rights Reserved

Available Formats

Download as PPT, PDF, TXT or read online from Scribd

Download as ppt, pdf, or txt

You are on page 1of 6

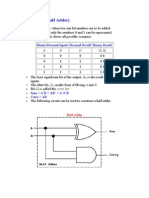

Half-Adder:

A combinational circuit which adds two one-bit binary

numbers is called a half-adder.

o The sum column resembles like an output of the XOR

gate.

o The carry column resembles like an output of the AND

gate.

Limitations (disadvantages) of half-adder:

o In multi-digit addition we have to add two bits

along with the carry of previous digit addition.

Such addition requires addition of 3 bits. This is

not possible in half-adders.

Full Adder:

o In a full adder, three bits can be added at a time. The

third bit is a carry from a less significant column.

Alternate Representation of Full-Adder:

Parallel Binary Adder

o While we add the LSB,

there is no carry to be

handled and thus, only a

half adder is used for this

stage.

o For any other bit addition,

there may be a carry from

the preceding stage and

thus, full adders are used

for these stages.

Example:

You might also like

- Installing and Cabling AWHxx AirScale Micro Remote Radio Heads 22R2 Issue-13 28062022Document158 pagesInstalling and Cabling AWHxx AirScale Micro Remote Radio Heads 22R2 Issue-13 28062022Yannick M.100% (1)

- 3 Bit AdderDocument11 pages3 Bit AdderAvirup DasguptaNo ratings yet

- DcuDocument3 pagesDcuAung MhNo ratings yet

- Half-Adder:: One-Bit Binary NumbersDocument6 pagesHalf-Adder:: One-Bit Binary Numbersrupa_13No ratings yet

- AddersDocument36 pagesAddersaditipatil2404No ratings yet

- Aim: Implement Full Adder and Subtractor Using VHDL Full AdderDocument2 pagesAim: Implement Full Adder and Subtractor Using VHDL Full AdderSaurabh AnandNo ratings yet

- Coa - Unit 4Document30 pagesCoa - Unit 4vishnuchandranrvNo ratings yet

- Full Adder Using Half AdderDocument4 pagesFull Adder Using Half AdderNiraj Shetty100% (1)

- Adder (Electronics)Document4 pagesAdder (Electronics)TurbosMixerNo ratings yet

- Binary Adders: AND Ex-OR A B SUM Carry Carry-OutDocument4 pagesBinary Adders: AND Ex-OR A B SUM Carry Carry-OutKrishna AgarwalNo ratings yet

- Unit 1 (1) Physics EngineeringDocument26 pagesUnit 1 (1) Physics EngineeringShiny ShinyNo ratings yet

- COA Textbook by DGMITDocument62 pagesCOA Textbook by DGMITI AM Hemant TankNo ratings yet

- Digital Logic8Document27 pagesDigital Logic8priyanka vsNo ratings yet

- Full Subtractor: Block DiagramDocument5 pagesFull Subtractor: Block DiagramLans KabaNo ratings yet

- Binary Adder SubstractorDocument4 pagesBinary Adder SubstractorRam samplaNo ratings yet

- Half Adder and Full AdderDocument6 pagesHalf Adder and Full AdderGreat OhaekwusiNo ratings yet

- STLD Unit IIIDocument29 pagesSTLD Unit IIIsnow54685No ratings yet

- Adder-Subtracter: Digital Circuits Adding Subtracting BinaryDocument8 pagesAdder-Subtracter: Digital Circuits Adding Subtracting BinaryPathan SaifNo ratings yet

- 202004021910157352aksingh Phy Adder SubtractorDocument8 pages202004021910157352aksingh Phy Adder SubtractorJai SrivastavaNo ratings yet

- Digital Logic CircuitDocument15 pagesDigital Logic CircuitCVCS OfficialNo ratings yet

- 6 - Combinational CurcuitDocument38 pages6 - Combinational CurcuitPlay StoreNo ratings yet

- Fun of DEDocument35 pagesFun of DETonmoy ChowdhuryNo ratings yet

- Half Adder BAsics, Full Adder BAsicsDocument15 pagesHalf Adder BAsics, Full Adder BAsicsz33sha9No ratings yet

- Unit-Iv Adders:: Binary Adder Notations and OperationsDocument33 pagesUnit-Iv Adders:: Binary Adder Notations and OperationsRene DevNo ratings yet

- L13 Parallel AddersDocument11 pagesL13 Parallel AddersVishnu MaskarNo ratings yet

- Unit 3Document34 pagesUnit 3Brooke DNo ratings yet

- Difference Between Half Adder and Full Adder12568978 PDFDocument1 pageDifference Between Half Adder and Full Adder12568978 PDFAnonymous a8rdyKOCNo ratings yet

- Digitallogicdesign2 160527173208Document304 pagesDigitallogicdesign2 160527173208m.raifanaufar01No ratings yet

- AddersDocument5 pagesAddersShanuj GargNo ratings yet

- Binary Adder: Adder. A Basic Binary Adder Circuit Can Be Made From StandardDocument10 pagesBinary Adder: Adder. A Basic Binary Adder Circuit Can Be Made From StandardJohn Brix BalisterosNo ratings yet

- Objective:: About ModelsimDocument9 pagesObjective:: About ModelsimZakria AlamNo ratings yet

- Booth MultiplierDocument5 pagesBooth Multiplierrahul rNo ratings yet

- Parallel Binary Adders: ScriptDocument9 pagesParallel Binary Adders: Scriptirfan ansariNo ratings yet

- Module 3Document47 pagesModule 3beebeefathimabagum435No ratings yet

- Chapter 4 - Digital LogicDocument19 pagesChapter 4 - Digital Logicvc78it10No ratings yet

- ALU Report by SameerDocument8 pagesALU Report by SameerSaad ZulfiqarNo ratings yet

- Technical College Information System Engineering: First ClassDocument13 pagesTechnical College Information System Engineering: First ClassDler AhmadNo ratings yet

- Arithmatic CircuitDocument7 pagesArithmatic CircuitsardarzaibibalochNo ratings yet

- Lecture 12 Binary Adder-SubtractorDocument8 pagesLecture 12 Binary Adder-SubtractorSasi Kiran SNo ratings yet

- Explain Half Adder and Full Adder With Truth TableDocument6 pagesExplain Half Adder and Full Adder With Truth TableMuhammad AwaisNo ratings yet

- Biteranta CsoworkDocument13 pagesBiteranta Csoworkapi-619829083No ratings yet

- Binary Adder: A Full Adder CircuitDocument8 pagesBinary Adder: A Full Adder CircuitSejal KankriyaNo ratings yet

- Computer Organization and Architecture: UNIT-2Document29 pagesComputer Organization and Architecture: UNIT-2CloudNo ratings yet

- Complete COA 2nd UnitDocument97 pagesComplete COA 2nd UnitishitaNo ratings yet

- Half Adder: Block DiagramDocument13 pagesHalf Adder: Block DiagramArunkumar VjNo ratings yet

- Mod3 Part 2Document81 pagesMod3 Part 2Sherine SebastianNo ratings yet

- Booth's, Barrel's and Array MultiplicationDocument7 pagesBooth's, Barrel's and Array MultiplicationJyothendranadh SaiNo ratings yet

- DEC Report 4 (C)Document11 pagesDEC Report 4 (C)S M Akash100% (1)

- 1-Bit Adder (Half Adder) : Binary/Decimal Inputs Decimal Result Binary ResultDocument4 pages1-Bit Adder (Half Adder) : Binary/Decimal Inputs Decimal Result Binary ResultmothilalbukyaNo ratings yet

- Assembly PracDocument6 pagesAssembly PracramevsNo ratings yet

- Parallel SubtractorDocument2 pagesParallel SubtractorParineeti KhanNo ratings yet

- Brent Kung AdderDocument74 pagesBrent Kung AdderVinay ReddyNo ratings yet

- ECE - 1551 Digital Logic Lecture 15: Combinational Circuits: Assistant Prof. Fareena SaqibDocument19 pagesECE - 1551 Digital Logic Lecture 15: Combinational Circuits: Assistant Prof. Fareena SaqibAll aboutNo ratings yet

- Explain Half Adder and Full Adder With Truth TableDocument28 pagesExplain Half Adder and Full Adder With Truth TableJayvee ColiaoNo ratings yet

- Practical: 3 Aim: Implement Common Bus System of Four 4-Bit Register Using 2x4 Decoder and Three State BufferDocument2 pagesPractical: 3 Aim: Implement Common Bus System of Four 4-Bit Register Using 2x4 Decoder and Three State BufferMahesh Pillai100% (2)

- Combinational Circuit Is A Circuit in Which We Combine The Different Gates in The CircuitDocument13 pagesCombinational Circuit Is A Circuit in Which We Combine The Different Gates in The Circuitalvin castroNo ratings yet

- Combinational Circuits DesignDocument32 pagesCombinational Circuits DesignRudra ChauhanNo ratings yet

- Adder CircuitDocument3 pagesAdder CircuitOchi Frank EribaNo ratings yet

- Department of Ece Ec T45 - Digital Circuits Unit - 3Document41 pagesDepartment of Ece Ec T45 - Digital Circuits Unit - 3thiruct77No ratings yet

- 4bit Array MultiplierDocument4 pages4bit Array MultiplierRahul TiwariNo ratings yet

- Experiment-5: Aim: Implement 4-Bit Parallel Adder Parallel Binary AddersDocument1 pageExperiment-5: Aim: Implement 4-Bit Parallel Adder Parallel Binary AddersSaurabh AnandNo ratings yet

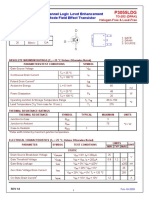

- p3055ldg NikoDocument4 pagesp3055ldg NikoАлексей ГомоновNo ratings yet

- Service Manual: PCG-GRS150/GRS170Document12 pagesService Manual: PCG-GRS150/GRS170Andrei RadulescuNo ratings yet

- Battery Catalogue 2014Document84 pagesBattery Catalogue 2014Chiranjivi Kuthumi100% (1)

- CT 25 L 8 GDocument20 pagesCT 25 L 8 GkosmitoNo ratings yet

- Dok TD MRD1 GeDocument56 pagesDok TD MRD1 GeheriberhuertaNo ratings yet

- The RBS 6000 SeriesDocument138 pagesThe RBS 6000 Seriesmola argawNo ratings yet

- URCO Series Ultimate RCO: Now For Systems With Run Capacitors!Document2 pagesURCO Series Ultimate RCO: Now For Systems With Run Capacitors!corrales_86No ratings yet

- Solar TrackerDocument38 pagesSolar TrackerAnonymous ytZsBOVNo ratings yet

- Up Lab ManualDocument57 pagesUp Lab ManualDeepak SharmaNo ratings yet

- Unit-Iii Engine Auxiliary Systems: Fuel Feed SystemDocument26 pagesUnit-Iii Engine Auxiliary Systems: Fuel Feed SystemMuthuvel MNo ratings yet

- Sample Exam 1 EE 210Document6 pagesSample Exam 1 EE 210doomachaleyNo ratings yet

- Experiment 1Document17 pagesExperiment 1Eng.Mohammed ReyadNo ratings yet

- Blue'log X Series: Operating ManualDocument124 pagesBlue'log X Series: Operating ManualArianit ZeqiriNo ratings yet

- Digiflex KMTDocument58 pagesDigiflex KMTsarafciger12350% (2)

- Cisco Epc 3925Document106 pagesCisco Epc 3925Michael L. MadsenNo ratings yet

- Wheatstone BridgeDocument13 pagesWheatstone Bridgeshawky allam100% (2)

- GT210-10 NGR W TransformerDocument2 pagesGT210-10 NGR W TransformerDeepen SharmaNo ratings yet

- The Good OneDocument5 pagesThe Good Oneapi-379298286No ratings yet

- Microsoft Word - Smart Grid Initiatives in India - Final PaperDocument15 pagesMicrosoft Word - Smart Grid Initiatives in India - Final PaperE.AvinashNo ratings yet

- Presentation MikrotikDocument43 pagesPresentation Mikrotikmarco antonio martinez andradeNo ratings yet

- Aguado Measurement 1Document6 pagesAguado Measurement 1HADHI HASSAN KHANNo ratings yet

- BTS3912E Product Description 01 (20161102)Document27 pagesBTS3912E Product Description 01 (20161102)Ahmed Salah MohmedNo ratings yet

- Vol.2C Technical Specifications DistributionDocument305 pagesVol.2C Technical Specifications DistributionExports Trafo PowerNo ratings yet

- PGVAC4036MOBILE02Document2 pagesPGVAC4036MOBILE02aidin.ashtariNo ratings yet

- Zero Crossing Detection Using Comparator Circuit: Analog Engineer's Circuit: AmplifiersDocument5 pagesZero Crossing Detection Using Comparator Circuit: Analog Engineer's Circuit: AmplifiersNg MeriedNo ratings yet

- Sc20Mpc: Spinel 2MP Serial JPEG Color CameraDocument2 pagesSc20Mpc: Spinel 2MP Serial JPEG Color CameramhasansharifiNo ratings yet

- Noja 7478 00 Rc10 15 Osm200 User Guide WebDocument42 pagesNoja 7478 00 Rc10 15 Osm200 User Guide WebMarlon Jairo Serván FernándezNo ratings yet

- 4010-9825 24V Distribution Block Installation InstructionsDocument2 pages4010-9825 24V Distribution Block Installation InstructionsRobel MTNo ratings yet