Professional Documents

Culture Documents

Memory Interfacing

Memory Interfacing

Uploaded by

leenu123Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Memory Interfacing

Memory Interfacing

Uploaded by

leenu123Copyright:

Available Formats

Memory and Memory

Interfacing

Ajay Singh Raghuvanshi

Memory

Memory consists of a number of storage locations,

each of which is identified by a unique address

The ability of the CPU to identify each location is

known as its addressability

Each location stores a word i.e. the number of bits

that can be processed by the CPU in a single

operation. Word length may be typically 8,16, 24,

32, 64 or as many as 128 bits.

Memory Can be classified into two categories

RAM

ROM

Types of RAM memory

Static Random Access Memory (SRAM)

Doesn’t need refreshing ,Retains contents as long as power applied to the chip

Access time around 10 nanoseconds, Can be Used for cache memory

Dynamic Random Access Memory (DRAM)

Contents are constantly refreshed 1000 times per second

Access time 60 – 70 nanoseconds

Synchronous Dynamic Random Access Memory (SDRAM)

Quicker than DRAM

Access time less than 60 nanoseconds

Direct Rambus Dynamic Random Access Memory (DRDRAM)

New type of RAM architecture

Access time 20 times faster than DRAM, More expensive

Cache memory

Small amount of memory typically 256 or 512 kilobytes

Temporary store for often used instructions Faster for CPU to access than main memory

Level 1 cache is built within the CPU (internal) Level 2 cache may be on chip or nearby

(external)

Types of ROM

Programmable Read Only Memory (PROM)

Empty of data when manufactured

May be permanently programmed by the user

Erasable Programmable Read Only Memory (EPROM)

Can be programmed, erased and reprogrammed

The EPROM chip has a small window on top allowing it to be

erased by shining ultra-violet light on it

Afterreprogramming the window is covered to prevent new

contents being erased

Access time is around 45 – 90 nanoseconds

Types of ROM

Electrically Erasable Programmable Read Only Memory

(EEPROM)

Reprogrammed electrically without using ultraviolet light

Must be removed from the computer and placed in a special machine to

do this

Access times between 45 and 200 nanoseconds

Flash ROM

Similar to EEPROM

However, can be reprogrammed while still in the computer

Easier to upgrade programs stored in Flash ROM

Used to store programs in devices e.g. modems

Access time is around 45 – 90 nanoseconds

Typical RAM chip

Chip select 1 CS1

Chip select 2 CS2

Read RD 128 x 8 8-bit data bus

RAM

Write WR

7-bit address AD 7

CS1 CS2 RD WR Memory function State of data bus

0 0 x x Inhibit High-impedence

0 1 x x Inhibit High-impedence

1 0 0 0 Inhibit High-impedence

1 0 0 1 Write Input data to RAM

1 0 1 x Read Output data from RAM

1 1 x x

Typical ROM chip

Chip select 1 CS1

Chip select 2 CS2

512 x 8 8-bit data bus

ROM

9-bit address AD 9

Memory Interfacing

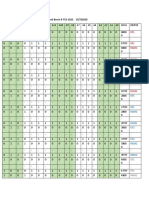

MEMORY ADDRESS MAP

Address space assignment to each

memory chip on a me

Example:

Hexa Address bus

Component address 10 9 8 7 6 5 4 3 2 1

RAM 1 0000 - 007F 0 0 0 x x x x x x x

RAM 2 0080 - 00FF 0 0 1 x x x x x x x

RAM 3 0100 - 017F 0 1 0 x x x x x x x

RAM 4 0180 - 01FF 0 1 1 x x x x x x x

1 x x x x x x x x x

ROM 0200 - 03FF

The 74LS138, 3-to-8 line decoder

Example: Design a 64K-8 EPROM interface for the 8086 microprocessor

using EPROM chips (8K x 8). The ROM memory starts at address F0000H-

FFFFFH.

Assignment 2

Design memory interface to be used with

MPU 8086 in Minimum mode with

following specifications

ROM : 128 K: using 8 ROM chips of same size

RAM : 256 K: using 8 RAM chips of same size

Draw the memory map of the system showing

the chip address range for each chip

Memory Map For problem

A19 A18 A17 A16 A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 Address Range Chip No

1 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 F0000

ROM1

1 1 1 1 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 F0FFF

1 1 1 1 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 F1000

ROM2

1 1 1 1 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 F1FFF

1 1 1 1 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 F2000

ROM3

1 1 1 1 0 0 1 0 1 1 1 1 1 1 1 1 1 1 1 1 F2FFF

1 1 1 1 0 0 1 1 0 0 0 0 0 0 0 0 0 0 0 0 F3000

ROM4

1 1 1 1 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 F3FFF

1 1 1 1 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 F4000

ROM5

1 1 1 1 0 1 0 0 1 1 1 1 1 1 1 1 1 1 1 1 F4FFF

1 1 1 1 0 1 0 1 0 0 0 0 0 0 0 0 0 0 0 0 F5000

ROM6

1 1 1 1 0 1 0 1 1 1 1 1 1 1 1 1 1 1 1 1 F5FFF

1 1 1 1 0 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 F6000

ROM7

1 1 1 1 0 1 1 0 1 1 1 1 1 1 1 1 1 1 1 1 F6FFF

1 1 1 1 0 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 F7000

ROM8

1 1 1 1 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 F7FFF

1 1 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 F8000

RAM1

1 1 1 1 1 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 F8FFF

1 1 1 1 1 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 F9000

RAM2

1 1 1 1 1 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 F9FFF

1 1 1 1 1 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 FA000

RAM3

1 1 1 1 1 0 1 0 1 1 1 1 1 1 1 1 1 1 1 1 FAFFF

1 1 1 1 1 0 1 1 0 0 0 0 0 0 0 0 0 0 0 0 FB000

RAM4

1 1 1 1 1 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 FBFFF

1 1 1 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 FC000

RAM5

1 1 1 1 1 1 0 0 1 1 1 1 1 1 1 1 1 1 1 1 FCFFF

1 1 1 1 1 1 0 1 0 0 0 0 0 0 0 0 0 0 0 0 FD000

RAM6

1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 1 1 1 1 1 FDFFF

1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 FE000

RAM7

1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 1 1 1 1 FEFFF

1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 FF000

RAM8

1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 FFFFF

You might also like

- Me7.1 - Me7.5 - Bosch SchemaDocument1 pageMe7.1 - Me7.5 - Bosch Schemadorcky100% (1)

- 01 Chapter-03 Memory InterfacingDocument4 pages01 Chapter-03 Memory Interfacingrebel8491No ratings yet

- Chapter 1 - Fundamental of MicrocontrollerDocument29 pagesChapter 1 - Fundamental of Microcontrollerpham tamNo ratings yet

- Chapter 1 - Fundamental of MicrocontrollerDocument30 pagesChapter 1 - Fundamental of MicrocontrollerminhkhoaNo ratings yet

- 8086 - Memory InterfacingDocument5 pages8086 - Memory InterfacingRocky SamratNo ratings yet

- VEBYARISKADocument6 pagesVEBYARISKAChristein PangandahengNo ratings yet

- Arsitektur Komputer 4Document4 pagesArsitektur Komputer 4Christein PangandahengNo ratings yet

- 8086 and Memory Interfacing - FinalDocument28 pages8086 and Memory Interfacing - FinalAnushkaSinha100% (2)

- Memory and Memory Interfacing: Ajay Singh RaghuvanshiDocument13 pagesMemory and Memory Interfacing: Ajay Singh Raghuvanshiiec2011007No ratings yet

- Problema Diseño de Circuitos DigitalesDocument3 pagesProblema Diseño de Circuitos Digitalesjosebroce4No ratings yet

- PemetaanDocument3 pagesPemetaanGerald MamangkeyNo ratings yet

- Lecture 22-Indirect AddressingDocument36 pagesLecture 22-Indirect AddressingHassan ShehadiNo ratings yet

- MemoryDocument33 pagesMemoryali vaisiNo ratings yet

- Memory & I/O AddressingDocument13 pagesMemory & I/O AddressingMonisha AdhikaryNo ratings yet

- Module 7: Memory Interfacing: Cs/Ece/Eee/Instr F241 - Microprocessor Programming & InterfacingDocument4 pagesModule 7: Memory Interfacing: Cs/Ece/Eee/Instr F241 - Microprocessor Programming & InterfacingsanaullahNo ratings yet

- Using U-Boot To Boot From A NAND Flash Memory Device For MPC8313EDocument20 pagesUsing U-Boot To Boot From A NAND Flash Memory Device For MPC8313EaledangieNo ratings yet

- Memory Organization and Interfacing EEE-3131Document13 pagesMemory Organization and Interfacing EEE-3131ShazidNo ratings yet

- 2b Prof. Shabiul Lecture Ch-2 2 Octo 2023Document38 pages2b Prof. Shabiul Lecture Ch-2 2 Octo 2023j2yshjzzsxNo ratings yet

- cs502snscm4 PDFDocument26 pagescs502snscm4 PDFTheStupidityOfPplNo ratings yet

- The Central Processing Unit (CPU) : Bayan University For Science & TechnologyDocument56 pagesThe Central Processing Unit (CPU) : Bayan University For Science & TechnologyAltayeb AbdulhameedNo ratings yet

- PLD Va He Tuan Tu Dong BoDocument29 pagesPLD Va He Tuan Tu Dong BoHiếu Nguyễn MinhNo ratings yet

- Microprocessor Lecture 5 FullDocument25 pagesMicroprocessor Lecture 5 Fullnoway snirfyNo ratings yet

- PLD Course Notes Unit-5 PDFDocument28 pagesPLD Course Notes Unit-5 PDFLenon AndetklNo ratings yet

- Gimi v48k9k89k5Document24 pagesGimi v48k9k89k5Mihai DespotoviciNo ratings yet

- 8051 InterfacingDocument6 pages8051 Interfacingravi sainiNo ratings yet

- 8051Document161 pages805121wh1a0487No ratings yet

- Site Save of CodeSlinger - Co.uk - GameBoy Emulator Programming in C++ - MemoryDocument3 pagesSite Save of CodeSlinger - Co.uk - GameBoy Emulator Programming in C++ - MemoryRyanNo ratings yet

- Ghost ErrDocument12 pagesGhost ErrAriesscremmo Gokiel UyeeNo ratings yet

- Address Decoding TechniqueDocument8 pagesAddress Decoding TechniqueYash SarohaNo ratings yet

- PDF Created With Fineprint Pdffactory Trial VersionDocument1 pagePDF Created With Fineprint Pdffactory Trial Versionganeshkamath89No ratings yet

- DF GTU Study Material Presentations Unit-5Document44 pagesDF GTU Study Material Presentations Unit-5bhavanitelecom123No ratings yet

- Memory InterfacingDocument6 pagesMemory InterfacingManish Kumar NaikNo ratings yet

- Nand SPLDocument20 pagesNand SPLsageson_m-1No ratings yet

- Edgerouter ConsoleDocument4 pagesEdgerouter ConsoleGreg JasNo ratings yet

- Writing To Flash and Eeprom On The Tinyavr 1-Series: Application NoteDocument11 pagesWriting To Flash and Eeprom On The Tinyavr 1-Series: Application NoteanilNo ratings yet

- Memory InterfacingDocument9 pagesMemory InterfacingPiyush chaudhariNo ratings yet

- Ec 1201digital ElectronicsDocument17 pagesEc 1201digital ElectronicsSubathra Devi MourouganeNo ratings yet

- BMW Bosch Edc17c06 Bench Fullbackup 20240423161527 HistoryDocument2 pagesBMW Bosch Edc17c06 Bench Fullbackup 20240423161527 HistoryAdrian NegoiNo ratings yet

- Lecture 5 - Ece521 Instruction Sets - Data TranfersDocument34 pagesLecture 5 - Ece521 Instruction Sets - Data TranfersAmar MursyidNo ratings yet

- Memory - IO - 8255 InterfacingDocument27 pagesMemory - IO - 8255 Interfacingashi.s300403No ratings yet

- Lecture14-8085 Memory InterfacingDocument18 pagesLecture14-8085 Memory InterfacingSaurabh BhiseNo ratings yet

- Basic Configuration of M-DC-SeriesDocument19 pagesBasic Configuration of M-DC-SeriesOnne RS-EmpireNo ratings yet

- Slides 2Document35 pagesSlides 2Mohamed AyedNo ratings yet

- PCDocument25 pagesPCPrasun BiswasNo ratings yet

- Tutorial - 9Document15 pagesTutorial - 9divyarai12345No ratings yet

- CPU-Z HTML Report FileDocument28 pagesCPU-Z HTML Report FilephanipriyankNo ratings yet

- Chapter 4: Interfacing MemoryDocument6 pagesChapter 4: Interfacing MemoryAbhinav ChuttaniNo ratings yet

- Assignment # 3 CHAPTERS# 1,2,3: CH#1 Answers To Review Qestions SECTION 1.1Document34 pagesAssignment # 3 CHAPTERS# 1,2,3: CH#1 Answers To Review Qestions SECTION 1.1Naheed HameedNo ratings yet

- 8052 PROGRAMMING TutorialsDocument30 pages8052 PROGRAMMING Tutorialsapi-26695410100% (2)

- Microprocessor 03 04Document82 pagesMicroprocessor 03 04Nuzhat AfrinNo ratings yet

- 8086 Memory & Interfacing PDFDocument39 pages8086 Memory & Interfacing PDFAnnamalai SelvarajanNo ratings yet

- Chapter Four: Memory OrganizationDocument16 pagesChapter Four: Memory OrganizationbelihuNo ratings yet

- Flash MemoriesDocument52 pagesFlash MemoriesJeff GicharuNo ratings yet

- Chapter 4Document20 pagesChapter 4salitemhiretNo ratings yet

- CSA Lab Report 2Document5 pagesCSA Lab Report 2Sadat AminNo ratings yet

- DLD V UnitDocument20 pagesDLD V UnitBHARATH KAMASANINo ratings yet

- 04Document22 pages04raulleite91No ratings yet

- RAM 2522 DKDocument40 pagesRAM 2522 DKDon Nipuna PandithasundaraNo ratings yet

- Sheet 5Document10 pagesSheet 5anoop_383575% (8)

- Neo Geo Architecture: Architecture of Consoles: A Practical Analysis, #23From EverandNeo Geo Architecture: Architecture of Consoles: A Practical Analysis, #23No ratings yet

- Instruction Set ArchitectureDocument33 pagesInstruction Set Architectureleenu123No ratings yet

- Microprocessor and Programming: Visit For More Learning ResourcesDocument39 pagesMicroprocessor and Programming: Visit For More Learning Resourcesleenu123No ratings yet

- Micron Internship Program Application Form: 申請日期 Date:西元 年 (Y) 月 (M) 日 (D)Document3 pagesMicron Internship Program Application Form: 申請日期 Date:西元 年 (Y) 月 (M) 日 (D)leenu123No ratings yet

- Given That Show That, Has The Unique Solution: T, T T A T, T DT D D Z T Z Z T, T ' T ZDocument4 pagesGiven That Show That, Has The Unique Solution: T, T T A T, T DT D D Z T Z Z T, T ' T Zleenu123No ratings yet

- Sigma-Delta Modulator Simulation and Analysis Using MatlabDocument5 pagesSigma-Delta Modulator Simulation and Analysis Using Matlableenu123No ratings yet

- 14 Interpolation DecimationDocument32 pages14 Interpolation Decimationleenu123No ratings yet

- Sigma DeltaDocument30 pagesSigma Deltaleenu123No ratings yet

- Lab 4 - Tablespace & DatafileDocument18 pagesLab 4 - Tablespace & DatafilemsskjcNo ratings yet

- Branch: Computer Engineering Subject: Computer OrganizationDocument2 pagesBranch: Computer Engineering Subject: Computer Organizationmukulranag4No ratings yet

- PMAT 2000 Brochure PDFDocument2 pagesPMAT 2000 Brochure PDFbejiriveraNo ratings yet

- User Reference Manual Galaxy - A03sDocument103 pagesUser Reference Manual Galaxy - A03sHillHenderNo ratings yet

- The Zettabyte File System: Jeff Bonwick, Matt Ahrens, Val Henson, Mark Maybee, Mark ShellenbaumDocument13 pagesThe Zettabyte File System: Jeff Bonwick, Matt Ahrens, Val Henson, Mark Maybee, Mark ShellenbaumRijy LoranceNo ratings yet

- Computer Technology An IntroductionDocument184 pagesComputer Technology An Introductionapex tutorNo ratings yet

- Cambridge International AS & A Level: Computer Science 9618/11Document16 pagesCambridge International AS & A Level: Computer Science 9618/11Dylen WolffNo ratings yet

- R 2008 M.E. Embedded System Tech SyllabusDocument26 pagesR 2008 M.E. Embedded System Tech Syllabuslee_ganeshNo ratings yet

- Countcam 2 ManualDocument13 pagesCountcam 2 ManualDiego GuamánNo ratings yet

- CS101 Grand Quiz MCQSDocument8 pagesCS101 Grand Quiz MCQSHani KhanNo ratings yet

- HCSA-Presales-Storage V3.0 Training MaterialDocument102 pagesHCSA-Presales-Storage V3.0 Training MaterialMiguel GomesNo ratings yet

- WP Idc Report Nutanix Files Business ValueDocument16 pagesWP Idc Report Nutanix Files Business ValuegNo ratings yet

- RAID Types ExplainedDocument3 pagesRAID Types ExplainedBinu SivanNo ratings yet

- Uputstvo - Sony Dsc-w30Document0 pagesUputstvo - Sony Dsc-w30Стеван КовачNo ratings yet

- File Systems: Files Directories File System Implementation Example File SystemsDocument46 pagesFile Systems: Files Directories File System Implementation Example File SystemsSneha SheteNo ratings yet

- VSP MICROCODE VERSION 70-02-70-00/00 RELEASED 09/07/2011 Newly Supported Features and Functions For Version 70-02-70-00/00Document11 pagesVSP MICROCODE VERSION 70-02-70-00/00 RELEASED 09/07/2011 Newly Supported Features and Functions For Version 70-02-70-00/00mvhhbcNo ratings yet

- HLDS Double-Layer DVD Drive SpecsDocument5 pagesHLDS Double-Layer DVD Drive SpecsRJNo ratings yet

- User Manual of 4200Document284 pagesUser Manual of 4200kawashNo ratings yet

- Innodisk SATADOM-ML 3IE3 V2 DatasheetDocument2 pagesInnodisk SATADOM-ML 3IE3 V2 Datasheetkc9wscNo ratings yet

- SPARC Enterprise M8000/M9000 Servers: Overview GuideDocument64 pagesSPARC Enterprise M8000/M9000 Servers: Overview GuideRakesh SinghNo ratings yet

- IBM System Storage DS6800 DatasheetDocument8 pagesIBM System Storage DS6800 DatasheetAppalarajuNo ratings yet

- AF-DedupSecure Data Deduplication Based On Adaptive Dynamic Merkle Hash Forest PoW For Cloud StorageDocument11 pagesAF-DedupSecure Data Deduplication Based On Adaptive Dynamic Merkle Hash Forest PoW For Cloud Storageunwell.whinny.0zNo ratings yet

- CHS Module 1 - Installing Computer Systems and NetworksDocument72 pagesCHS Module 1 - Installing Computer Systems and NetworksLawrence Cada Nofies100% (1)

- AaawsDocument16 pagesAaawsGiriprasad GunalanNo ratings yet

- CSE211 - Updated New IP Aug 2015Document26 pagesCSE211 - Updated New IP Aug 2015LakhanKadamNo ratings yet

- Free Space ManagementDocument19 pagesFree Space ManagementRehman ButtNo ratings yet

- Telegram Group: Answer Key Available atDocument17 pagesTelegram Group: Answer Key Available atabdul gani khanNo ratings yet

- CXL 2.0 Cache Mem Transaction and Link LayerDocument38 pagesCXL 2.0 Cache Mem Transaction and Link LayerKAJANo ratings yet

- Touchscreen ReportDocument40 pagesTouchscreen Reportbvkarthik2711No ratings yet

- Dual Control Data Storage DS-AD82 Series: Key FeaturesDocument3 pagesDual Control Data Storage DS-AD82 Series: Key FeaturesArioNo ratings yet