Professional Documents

Culture Documents

Memory System

Memory System

Uploaded by

Govindaraju Mariyappan0 ratings0% found this document useful (0 votes)

66 views20 pagesOriginal Title

MEMORY SYSTEM

Copyright

© Attribution Non-Commercial (BY-NC)

Available Formats

PPTX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as PPTX, PDF, TXT or read online from Scribd

Download as pptx, pdf, or txt

0 ratings0% found this document useful (0 votes)

66 views20 pagesMemory System

Memory System

Uploaded by

Govindaraju MariyappanCopyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as PPTX, PDF, TXT or read online from Scribd

Download as pptx, pdf, or txt

You are on page 1of 20

MEMORY SYSTEM

INTERNAL ORGANIZATION OF MEMORY

CHIPS

• Memory cells are usually organized in the

form of an array, in which each cell is capable

of storing one bit of information.

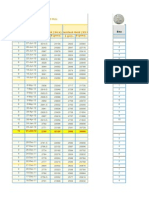

• Figure 2. Organization of bit cells in a memory

chip.

• Each row of cells constitutes a memory word,

and all cells of a row are connected to a

common line referred to as the word line,

which is driven by the address decoder on the

chip. The cells in each column are connected

to a Sense/Write circuit by two bit lines.

• The Sense/Write circuits are connected to the

data input/output lines of the chip.

• During a Read operation, these circuits

sense, or read the information stored in the

cells selected by a word line and transmit this

information to the output data lines.

• During a Write operation, the sense/ Write

circuits receive input information and store it

in the cells of the selected word.

• Above fig is an example of a very small

memory chip consisting of 16 words of 8 bits

each. This is referred to as a 16*8

organization. The data input and the data

output of each sense/write circuit are

connected to a single bidirectional data line

that can be connected to the data bus of a

computer.

• Two control lines, R/W and CS, are provided in

addition to address and data lines. The R/W

(Read/Write) input specifies the required

operation, and the CS (Chip Select) input

selects a given chip in a multi chip memory

system.

• The memory circuit in above diagram stores

128 bits and requires 14 external connections

for address, data and control lines. It also

needs two lines for power supply and ground

connections. Consider now a slightly larger

memory circuit, one that has 1K (1024)

memory cells. This circuit can be organized as

a 128*8 memory requiring a total of 19

external connections.

Organization of a 1K × 1 memory

• Alternatively, the same number of cells can be

organized into a 1K*1 format. In this case, a 10

bit address is needed but there is only one

data line, resulting in 15 external connections

is shown below,

• The required 10 bit address is divided into two

groups of 5 bits each to form the row and

column addresses for the cell array. A row

address selects a row of 32 cells, all of which

are accessed in parallel. However, according to

the column address, only one of these cells is

connected to the external data line by the

output multiplexer and input demultiplexer

MEMORIES

• STATIC MEMORIES

• DYNAMIC MEMORIES

STATIC MEMORIES

• Memories that consist of circuits capable of

retaining their state as long as power is

applied are known as static memories.

• Below diagram illustrates how a static RAM

(SRAM) cell may be implemented.

• Two inverters are cross connected to form a

latch. The latch is connected to two bit lines

by transistors T1 and T2. These transistors act

as switches that can be opened or closed

under control of the word line. When the

word line is at ground level, the transistors are

turned off and the latch retains its state.

• For example, if the cell is in state 1 then the

value at point X is 1. If the cell is in state 0

then the value at point Y is 0. This state is

maintained as long as the signal on the word

line is at ground level.

• Read Operation:

• In order to read the state of the SRAM cell, the

word line is activated to close switches T1 and

T2.

• If the cell is in state 1, then the signal on bit line

b is high and the signal on bit line b’ is low.

• If the cell is in state 0, then the signal on bit line

b is low and the signal on bit line b’ is high.

• Write Operation:

• The state of the cell is set by placing the

appropriate value on bit line b and its

complement on b’, and then activating the

word line. This forces the cell into the

corresponding state. The required signal on

the bit lines are generated by the Sense/Write

circuit.

• ASYNCHRONOUS DRAMS

• Static RAM are fast, but they come at a high

cost because their cells require several

transistors. Less expensive RAMs can be

implemented if simpler cells are used. Such

cells do not retain their state indefinitely;

hence, they are called dynamic RAMs

(DRAMs).

DRAM

• Information is stored in a dynamic memory

cell in the form of a charge on a capacitor, and

this charge can be maintained for only tens of

milliseconds. Since the cell is required to store

information for a much longer time, its

contents must be periodically refreshed by

restoring the capacitor charge to its full value.

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5823)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1093)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (852)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (898)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (540)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (349)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (823)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (403)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- a拉扎维模拟CMOS集成电路第二版最新答案Document1,603 pagesa拉扎维模拟CMOS集成电路第二版最新答案就爱吃饭团No ratings yet

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Hspice Simulation of SRAMDocument65 pagesHspice Simulation of SRAMYatheesh Kaggere100% (1)

- 1 GRM 8 Grms. 1 Grm. 8 Grms. Sno Date Pure Gold (24 K) Standard Gold (22 K)Document4 pages1 GRM 8 Grms. 1 Grm. 8 Grms. Sno Date Pure Gold (24 K) Standard Gold (22 K)Govindaraju MariyappanNo ratings yet

- 1 GRM 8 Grms. 1 Grm. 8 Grms. Sno Date Pure Gold (24 K) Standard Gold (22 K)Document4 pages1 GRM 8 Grms. 1 Grm. 8 Grms. Sno Date Pure Gold (24 K) Standard Gold (22 K)Govindaraju MariyappanNo ratings yet

- CS1354 GMDocument7 pagesCS1354 GMGovindaraju MariyappanNo ratings yet

- Temperature Controller BasicDocument33 pagesTemperature Controller BasicGovindaraju MariyappanNo ratings yet

- E Gas SewaDocument2 pagesE Gas SewasizzlinggeethuNo ratings yet

- Introduction To FET-Field Effect TransistorDocument2 pagesIntroduction To FET-Field Effect TransistorRushikesh TrimbakeNo ratings yet

- Semiconductor Devices-Module-4 PDFDocument36 pagesSemiconductor Devices-Module-4 PDFNishant KumarNo ratings yet

- Driver Tyristor and TransistorDocument11 pagesDriver Tyristor and TransistorEduard KeynesNo ratings yet

- Transistor MOSFET - K3767Document6 pagesTransistor MOSFET - K3767David Jonatan Alayo LlajarunaNo ratings yet

- Eee421: Power Electronics: Power Semiconductor Devices: MOSFETDocument9 pagesEee421: Power Electronics: Power Semiconductor Devices: MOSFETRafat ShamsNo ratings yet

- CH 11Document34 pagesCH 11Ken Dela CernaNo ratings yet

- Data Sheet: N-Channel Enhancement Mode MOS TransistorDocument8 pagesData Sheet: N-Channel Enhancement Mode MOS TransistorArgenis VeraNo ratings yet

- Lab1 Tranzistoare EngDocument11 pagesLab1 Tranzistoare Engtoufik bendibNo ratings yet

- Microproject BJT GPSAKOLI 2Document14 pagesMicroproject BJT GPSAKOLI 2Vaibhav JadhavNo ratings yet

- Crawford MOSFET in Circuit Design 1967Document162 pagesCrawford MOSFET in Circuit Design 1967Nikolas AugustoNo ratings yet

- Standby Leakage Power Reduction in Digital CircuitsDocument4 pagesStandby Leakage Power Reduction in Digital CircuitsmadhuNo ratings yet

- Silicon N-Channel Power F-MOS FETDocument3 pagesSilicon N-Channel Power F-MOS FETANDREASBOULNo ratings yet

- With Help From David Szmyd, Silicon LabsDocument38 pagesWith Help From David Szmyd, Silicon LabsYidnekachwe MekuriaNo ratings yet

- DataSheet - PA410BDDocument8 pagesDataSheet - PA410BDastartngNo ratings yet

- Bipolar Junction Transistor (BJT) - Part 2Document31 pagesBipolar Junction Transistor (BJT) - Part 2Khánh ĐỗNo ratings yet

- Thyristors and Triacs PDFDocument30 pagesThyristors and Triacs PDFCristianNo ratings yet

- CS220N04 A8H: Silicon N-Channel Power MOSFETDocument10 pagesCS220N04 A8H: Silicon N-Channel Power MOSFETminreyNo ratings yet

- Modified Gate Diffusion Input Technique: A New Technique For Enhancing Performance in Full Adder CircuitsDocument8 pagesModified Gate Diffusion Input Technique: A New Technique For Enhancing Performance in Full Adder CircuitsPhoenixinnovations supportNo ratings yet

- DC Transfer Characteristics of InverterDocument5 pagesDC Transfer Characteristics of InverterKeerthan .R.VarmaNo ratings yet

- P5506BDG UnikcDocument5 pagesP5506BDG UnikcYessenia PerezNo ratings yet

- Silicon Controlled Rectifier (SCR) : Case (I) : When Gate Is Open. Figure Shows The SCR Circuit With Gate Open I.E. NoDocument4 pagesSilicon Controlled Rectifier (SCR) : Case (I) : When Gate Is Open. Figure Shows The SCR Circuit With Gate Open I.E. NoansonNo ratings yet

- WFF7N60 WisdomtechnologiesDocument7 pagesWFF7N60 WisdomtechnologiesAlejandro Ivan AbelikNo ratings yet

- FET AC Analysis PDFDocument20 pagesFET AC Analysis PDFnupur kesarwaniNo ratings yet

- Switch Level ModelingDocument8 pagesSwitch Level Modelingsindhuja selvamNo ratings yet

- Impact of MOSFET's Performance On Its Threshold Voltage and Its in Uence On Design of MOS InvertersDocument11 pagesImpact of MOSFET's Performance On Its Threshold Voltage and Its in Uence On Design of MOS InvertersgkNo ratings yet

- Model Question PaperDocument1 pageModel Question PaperV SATYA KISHORENo ratings yet

- Module II Shrink Down ApproachesDocument20 pagesModule II Shrink Down ApproachesArighna BasakNo ratings yet

- HFIC Chapter 4 HF TransistorsDocument77 pagesHFIC Chapter 4 HF TransistorsYosra Be100% (1)