Professional Documents

Culture Documents

Biasing Circuits of FET

Biasing Circuits of FET

Uploaded by

Monica Gunjal0 ratings0% found this document useful (0 votes)

96 views10 pagesThe document discusses voltage-divider bias circuits for field-effect transistors (FETs). It describes how the voltage-divider bias circuit works by using two resistors, Rg1 and Rg2, to form a potential divider across the drain supply voltage. This divides the voltage and provides the necessary bias voltage at the gate of the FET. The document also provides equations for calculating the quiescent drain current, gate-source voltage, and drain-source voltage of a JFET amplifier using this biasing method.

Original Description:

voltage divider bias circuit design using N CHANNEL JFET

Original Title

Biasing circuits of FET

Copyright

© © All Rights Reserved

Available Formats

PPTX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThe document discusses voltage-divider bias circuits for field-effect transistors (FETs). It describes how the voltage-divider bias circuit works by using two resistors, Rg1 and Rg2, to form a potential divider across the drain supply voltage. This divides the voltage and provides the necessary bias voltage at the gate of the FET. The document also provides equations for calculating the quiescent drain current, gate-source voltage, and drain-source voltage of a JFET amplifier using this biasing method.

Copyright:

© All Rights Reserved

Available Formats

Download as PPTX, PDF, TXT or read online from Scribd

Download as pptx, pdf, or txt

0 ratings0% found this document useful (0 votes)

96 views10 pagesBiasing Circuits of FET

Biasing Circuits of FET

Uploaded by

Monica GunjalThe document discusses voltage-divider bias circuits for field-effect transistors (FETs). It describes how the voltage-divider bias circuit works by using two resistors, Rg1 and Rg2, to form a potential divider across the drain supply voltage. This divides the voltage and provides the necessary bias voltage at the gate of the FET. The document also provides equations for calculating the quiescent drain current, gate-source voltage, and drain-source voltage of a JFET amplifier using this biasing method.

Copyright:

© All Rights Reserved

Available Formats

Download as PPTX, PDF, TXT or read online from Scribd

Download as pptx, pdf, or txt

You are on page 1of 10

Biasing circuits of FET

1. Fixed bias circuits

2. Self bias circuits

3. Voltage bias circuits

Voltage -Divider Bias circuits

Voltage -Divider Bias circuits

• The resistors RGl and RG2 form a potential divider across drain supply

VDD.

• The voltage V2 across RG2 provides the necessary bias.

• The additional gate resistor RGl from gate to supply voltage facilitates in

larger adjustment of the dc bias point and permits use of larger valued

RS.

• The coupling capacitors are assumed to be open circuit for DC analysis

Voltage -Divider Bias circuits

• The gate is reverse biased so that IG = 0 and gate voltage

VG = (VDD/R G1 + R G2 ) *RG2

• Applying KVL to the input circuit we get

VGS= VG – VS = VG - ID RS

IDQ= IDSS(1- VGS/ VP)2

VDS = VDD – ID (RD + RS)

• The operating point of a JFET amplifier using the Voltage -Divider Bias is determined by

IDQ= IDSS(1- VGS/ VP)2

VDSQ = VDD – ID (RD + RS)

VGSQ = VG – ID RS

Voltage -Divider Bias circuits

• Determine IDQ, VGSQ, VD, VS, VDS, and VDG

Example 2:

Example no.3

Calculate

You might also like

- Thesis Report FinalDocument25 pagesThesis Report FinalThanhha Nguyen100% (2)

- Indus Lab Exp 1Document12 pagesIndus Lab Exp 1plokplokplokNo ratings yet

- Lab 1Document4 pagesLab 1idasyarmilaNo ratings yet

- ABCD ParametersDocument3 pagesABCD ParametersKiranreddy BurriNo ratings yet

- Experiment No. - 5 EXPERIMENT NAME: To Determine Accurate Quality Factor of An Unknown Coil. TheoryDocument5 pagesExperiment No. - 5 EXPERIMENT NAME: To Determine Accurate Quality Factor of An Unknown Coil. TheoryDibyajit SenNo ratings yet

- Tutorial 1Document3 pagesTutorial 1dfsdsdfsdfsdfsdfsdNo ratings yet

- VI Characteristics of Gunn DiodeDocument2 pagesVI Characteristics of Gunn DiodePabasara ErangaNo ratings yet

- BEE LAB MANUAL FINAL1st SemesterDocument38 pagesBEE LAB MANUAL FINAL1st SemesterSaif KhanNo ratings yet

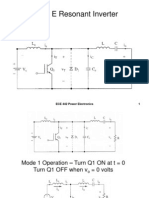

- Class E Resonant InverterDocument28 pagesClass E Resonant InverterSenthil Kumar0% (1)

- Single-Phase System (Resistive Load)Document20 pagesSingle-Phase System (Resistive Load)lalitbickNo ratings yet

- Ex. No.: 08: Go-Down WiringDocument5 pagesEx. No.: 08: Go-Down WiringamanNo ratings yet

- Experiment No.02 To Observe The Characteristics of A Half Wave RectifierDocument4 pagesExperiment No.02 To Observe The Characteristics of A Half Wave RectifierWaqas MughalNo ratings yet

- Diode Valve Effect: Electrical and Electronics LabDocument4 pagesDiode Valve Effect: Electrical and Electronics LabLare ONo ratings yet

- Report - Phase ShifterDocument8 pagesReport - Phase ShifterAmeer AliNo ratings yet

- Multistage AmplifiersDocument22 pagesMultistage AmplifiersParvinder SinghNo ratings yet

- Measurement of Resistance, Inductance and CapacitanceDocument64 pagesMeasurement of Resistance, Inductance and CapacitanceSiddhesh ShirshivkarNo ratings yet

- Power Amplifier Learning Objectives: The Small Signal Amplifiers We Studied Previously Are All Class A AmplifiersDocument9 pagesPower Amplifier Learning Objectives: The Small Signal Amplifiers We Studied Previously Are All Class A AmplifiersPascual Hilario ReNo ratings yet

- Lab ExperimentDocument6 pagesLab ExperimentWaseem Abbas100% (3)

- AE LAB - Experiment No.2-1Document4 pagesAE LAB - Experiment No.2-1Prajwal PatilNo ratings yet

- Temperatue and DiplacementDocument63 pagesTemperatue and Diplacementaregawi weleabezgi100% (1)

- ET Lab ManualDocument52 pagesET Lab Manualcholleti sriram100% (1)

- Measurement of High Voltages and High CurrentsDocument43 pagesMeasurement of High Voltages and High Currentssaikarthick023No ratings yet

- 09-Wien Bridge Oscillator Using OpAmp PDFDocument4 pages09-Wien Bridge Oscillator Using OpAmp PDFVishesh Kumar SinghNo ratings yet

- Clipper Clamper CircuitsDocument15 pagesClipper Clamper CircuitsAnilaSaghirNo ratings yet

- Analog Lab (EE2401) Experiment 2: GM-C FilterDocument10 pagesAnalog Lab (EE2401) Experiment 2: GM-C FilterFacebook securityNo ratings yet

- Andersons BridgeDocument3 pagesAndersons BridgeRamesh KumarNo ratings yet

- Construction of A 9V Power SupplyDocument7 pagesConstruction of A 9V Power SupplyCarroll SarmejeNo ratings yet

- Mosfet CharacteristicsDocument10 pagesMosfet CharacteristicsAnonymous eWMnRr70qNo ratings yet

- Finally Power DiodeDocument8 pagesFinally Power DiodeAndrei50% (2)

- Two Port Networks PPT 1 B TECH 3RDDocument32 pagesTwo Port Networks PPT 1 B TECH 3RDEuthecas KipkiruiNo ratings yet

- LED StructureDocument23 pagesLED StructureVISHNU KUSHWAHANo ratings yet

- Triangular Wave Generator Using Op Amp - WaveformsDocument6 pagesTriangular Wave Generator Using Op Amp - WaveformsNagendrababu VasaNo ratings yet

- Chapter 3: Ac Power AnalysisDocument40 pagesChapter 3: Ac Power AnalysisAtyia Javed100% (1)

- EXPT - 02 - Study of Single Stage BJT AmplifierxDocument5 pagesEXPT - 02 - Study of Single Stage BJT AmplifierxPrakash Narkhede100% (1)

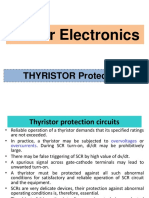

- Power Electronics: THYRISTOR ProtectionDocument12 pagesPower Electronics: THYRISTOR ProtectionK Lokesh LingaiahNo ratings yet

- Sample and Hold AssignmentDocument8 pagesSample and Hold AssignmentRen BurnettNo ratings yet

- Assignment 2-1Document2 pagesAssignment 2-1areejNo ratings yet

- Voltage & Current DividerDocument28 pagesVoltage & Current DividerArsal Javed ButtNo ratings yet

- Electronics Lecture Notes IIDocument31 pagesElectronics Lecture Notes IIWaltas KariukiNo ratings yet

- Experiment # 5Document7 pagesExperiment # 5Abdullah TahirNo ratings yet

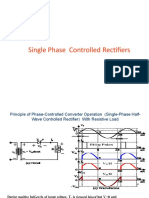

- Lecture 1-Single-Phase-Controlled-RectifiersDocument41 pagesLecture 1-Single-Phase-Controlled-RectifiersmadihaNo ratings yet

- Wireless Stepper Motor ControlDocument2 pagesWireless Stepper Motor ControlHarsha100% (1)

- Topics To Be Discussed: - Voltmeter Sensitivity. - Voltmeter LoadingDocument90 pagesTopics To Be Discussed: - Voltmeter Sensitivity. - Voltmeter LoadingPadarbinda SamalNo ratings yet

- Electronics Lab Exp3 PDFDocument17 pagesElectronics Lab Exp3 PDFgacc4sitesNo ratings yet

- Electrical Circuit Lab ManualDocument38 pagesElectrical Circuit Lab Manualecessec67% (3)

- ReportDocument30 pagesReportzabihuq100% (1)

- CH 3 - Controlled RectifiersDocument25 pagesCH 3 - Controlled RectifiersGebremichael Teklay GebretsadikNo ratings yet

- E.E.2.3.d.Parameters of Full Wave RectifierDocument5 pagesE.E.2.3.d.Parameters of Full Wave Rectifiernupur kesarwaniNo ratings yet

- Engineering Prob & Stat Lecture Notes 6Document12 pagesEngineering Prob & Stat Lecture Notes 6EICQ/00154/2020 SAMUEL MWANGI RUKWARONo ratings yet

- 40 Ei 4p2-Lic Lab ManualDocument94 pages40 Ei 4p2-Lic Lab ManualsoundsisterNo ratings yet

- Sumpner's TestDocument5 pagesSumpner's TestDina GaranNo ratings yet

- Lecture 2-KCL& KVL Nodal & Mesh Analysis.Document55 pagesLecture 2-KCL& KVL Nodal & Mesh Analysis.Ben MachariaNo ratings yet

- Government Polytechnic, Muzaffarpur: Name of The Lab: Electrical Workshop LabDocument15 pagesGovernment Polytechnic, Muzaffarpur: Name of The Lab: Electrical Workshop LabTapobroto Chatterjee100% (1)

- Electromagnetic Relay Static Relay Numerical Relay: Single Input Comparator Dual Input Comparator Multi Input ComparatorDocument34 pagesElectromagnetic Relay Static Relay Numerical Relay: Single Input Comparator Dual Input Comparator Multi Input ComparatorSathiyarajNo ratings yet

- Tube Light ManualDocument2 pagesTube Light ManualSwaroop MallickNo ratings yet

- Chap 11 Frequency - ResponseDocument173 pagesChap 11 Frequency - ResponseyashNo ratings yet

- 05 MOSFET Biasing EngDocument12 pages05 MOSFET Biasing Engsiddhant vermaNo ratings yet

- 05 MOSFET Biasing EngDocument12 pages05 MOSFET Biasing Engsiddhant vermaNo ratings yet

- CH 06 FET BiasingDocument20 pagesCH 06 FET BiasingHatem DheerNo ratings yet