Professional Documents

Culture Documents

Bits Pilani: Digital Systems (Combinational Circuit) Rktiwary Mano

Bits Pilani: Digital Systems (Combinational Circuit) Rktiwary Mano

Uploaded by

rktiwary256034Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Bits Pilani: Digital Systems (Combinational Circuit) Rktiwary Mano

Bits Pilani: Digital Systems (Combinational Circuit) Rktiwary Mano

Uploaded by

rktiwary256034Copyright:

Available Formats

BITS Pilani

Pilani Campus

DIGITAL systems (Combinational circuit)

RKTiwary

Mano

Chapter 4:

BITS Pilani, Deemed to be University under Section 3 of UGC Act, 1956

BCD Adder

+ x3 x2 x1 x0

4-bits plus 4-bits

Operands and Result: 0 to 9 + y3 y2 y1 y0

────────

X +Y x3 x2 x1 x0 y3 y2 y1 y0 Sum Cy S3 S2 S1 S0

Cy S3 S2 S1 S0

0+0 0 0 0 0 0 0 0 0 =0 0 0 0 0 0

0+1 0 0 0 0 0 0 0 1 =1 0 0 0 0 1

0+2 0 0 0 0 0 0 1 0 =2 0 0 0 1 0

0+9 0 0 0 0 1 0 0 1 =9 0 1 0 0 1

1+0 0 0 0 1 0 0 0 0 =1 0 0 0 0 1

1+1 0 0 0 1 0 0 0 1 =2 0 0 0 1 0

1+8 0 0 0 1 1 0 0 0 =9 0 1 0 0 1

1+9 0 0 0 1 1 0 0 1 =A 0 1 0 1 0 Invalid Code

2+0 0 0 1 0 0 0 0 0 =2 0 0 0 1 0

9+9 1 0 0 1 1 0 0 1 = 12 1 0 0 1 0 Wrong BCD Value

0001 1000

BITS Pilani, Deemed to be University under Section 3 of UGC Act, 1956

BCD Adder

X +Y x3 x2 x1 x0 y3 y2 y1 y0 Sum Cy S3 S2 S1 S0 Required BCD Output Value

9+0 1 0 0 1 0 0 0 0 =9 0 1 0 0 1 0 0 0 0 1 0 0 1 =9

9+1 1 0 0 1 0 0 0 1 = 10 0 1 0 1 0 0 0 0 1 0 0 0 0 = 16

9+2 1 0 0 1 0 0 1 0 = 11 0 1 0 1 1 0 0 0 1 0 0 0 1 = 17

9+3 1 0 0 1 0 0 1 1 = 12 0 1 1 0 0 0 0 0 1 0 0 1 0 = 18

9+4 1 0 0 1 0 1 0 0 = 13 0 1 1 0 1 0 0 0 1 0 0 1 1 = 19

9+5 1 0 0 1 0 1 0 1 = 14 0 1 1 1 0 0 0 0 1 0 1 0 0 = 20

9+6 1 0 0 1 0 1 1 0 = 15 0 1 1 1 1 0 0 0 1 0 1 0 1 = 21

9+7 1 0 0 1 0 1 1 1 = 16 1 0 0 0 0 0 0 0 1 0 1 1 0 = 22

9+8 1 0 0 1 1 0 0 0 = 17 1 0 0 0 1 0 0 0 1 0 1 1 1 = 23

9+9 1 0 0 1 1 0 0 1 = 18 1 0 0 1 0 0 0 0 1 1 0 0 0 = 24

+6

BITS Pilani, Deemed to be University under Section 3 of UGC Act, 1956

BCD Adder

Correct Binary Adder’s Output (+6)

▪ If the result is between ‘A’ and ‘F’

▪ If Cy = 1

S3 S2 S1 S0 Err

S1

0 0 0 0 0

1 0 0 0 0 S2

1 0 0 1 0 1 1 1 1

S3 1 1

1 0 1 0 1

S0

1 0 1 1 1

1 1 0 0 1

Err = S3 S2 + S3 S1

1 1 0 1 1

1 1 1 0 1

1 1 1 1 1 Err = C + S3 S2 + S3 S1

BITS Pilani, Deemed to be University under Section 3 of UGC Act, 1956

BCD Adder

x3 x2 x1 x0 y3 y2 y1 y0

A3 A2 A1 A0 B3 B2 B1 B0

Cy Binary Adder Ci 0

S3 S2 S1 S0

0 0

A3 A2 A1 A0 B3 B2 B1 B0

Cy Binary Adder Ci 0

S3 S2 S1 S0

Cy S3 S2 S1 S0

BITS Pilani, Deemed to be University under Section 3 of UGC Act, 1956

Binary Subtractor

Use 2’s complement with binary adder

▪ x – y = x + (-y) = x + y’ + 1

x3 x2 x1 x0 y3 y2 y1 y0

A3 A2 A1 A0 B3 B2 B1 B0

Cy Binary Adder Ci 1

S3 S2 S1 S0

F3 F2 F1 F0

BITS Pilani, Deemed to be University under Section 3 of UGC Act, 1956

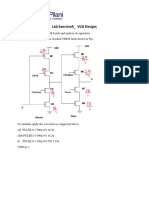

Binary Adder/Subtractor

M: Control Signal (Mode)

▪ M=0 F = x + y

▪ M=1 F = x – y

x3 x2 x1 x0 y3 y2 y1 y0 M

A3 A2 A1 A0 B 3 B2 B1 B0

Cy Binary Adder Ci

S3 S2 S1 S0

F3 F 2 F 1 F 0

BITS Pilani, Deemed to be University under Section 3 of UGC Act, 1956

2 Bit Binary Multiplier

BITS Pilani, Deemed to be University under Section 3 of UGC Act, 1956

Multiplicand 4 bit Multiplier 3 Bit

A bit of the multiplier is ANDed with

each bit of the multiplicand in as

many levels as there are bits in the

multiplier.

The binary output in each level of

AND gates is added with the partial

product of the previous level to form a

new partial product.

The last level produces the product.

For J multiplier bits and K

multiplicand bits,

We need J X K AND gates and

(J – 1) K -bit adders to produce a

product of (J + K) bits.

If there are more bits then instead of

HA , FA is used

BITS Pilani, Deemed to be University under Section 3 of UGC Act, 1956

MAGNITUDE COMPARATOR

𝐴 = 𝐴3 𝐴2 𝐴 1 𝐴 0 ; 𝐵 = 𝐵3 𝐵 2 𝐵1 𝐵0

Three outputs

)=

A

BITS Pilani, Deemed to be University under Section 3 of UGC Act, 1956

A3 ‘ B 3

A3B3 +A3’B3’

A3B3’

BITS Pilani, Deemed to be University under Section 3 of UGC Act, 1956

You might also like

- Advantages and Disadvantages of C4 Plant PhotosynthesisDocument5 pagesAdvantages and Disadvantages of C4 Plant PhotosynthesisAhsan Raza100% (1)

- Working Environment: Norsok StandardDocument52 pagesWorking Environment: Norsok StandardFoad MirzaieNo ratings yet

- Water and Slurry HammerDocument48 pagesWater and Slurry Hammeralvarezjgo100% (2)

- Janes Part1Document769 pagesJanes Part1Micoyan GurevichNo ratings yet

- Patrick Jordan 1998 PDFDocument9 pagesPatrick Jordan 1998 PDFFelipe Riolfi0% (1)

- Human Activities From Deliberate ReflectionDocument18 pagesHuman Activities From Deliberate ReflectionStephanie Castillon92% (12)

- Ix - Combinational Circuits (No Animation)Document19 pagesIx - Combinational Circuits (No Animation)Charles Brian LunasNo ratings yet

- Carry Look Ahead Adders: Lesson ObjectivesDocument10 pagesCarry Look Ahead Adders: Lesson ObjectivespadmavathiNo ratings yet

- BITS Pilani: Computer ProgrammingDocument42 pagesBITS Pilani: Computer ProgrammingkiranbitsNo ratings yet

- Adder Sub AluDocument22 pagesAdder Sub AluBasheer V.PNo ratings yet

- BCD AddedDocument16 pagesBCD AddedSuresh KumarNo ratings yet

- 16EI204 Digital Logic CircuitsDocument64 pages16EI204 Digital Logic CircuitsSanthoshkumar SethuramanNo ratings yet

- COE211 CH4 Combinational CircuitsDocument54 pagesCOE211 CH4 Combinational Circuitshm100hm100hm100No ratings yet

- Digital 5Document33 pagesDigital 5Soumyadip MoniNo ratings yet

- CMPUT329 - Fall 2003: Topic 4: Cost of Logic Circuits and Karnaugh MapsDocument88 pagesCMPUT329 - Fall 2003: Topic 4: Cost of Logic Circuits and Karnaugh MapsPrasad MullappillyNo ratings yet

- To Base by Summing The Expanded Notation. DDocument3 pagesTo Base by Summing The Expanded Notation. DAnonymous pjLkZPi9vNo ratings yet

- ALU 1 - Adder & Subtractor v2Document44 pagesALU 1 - Adder & Subtractor v2Barsha RoyNo ratings yet

- Combinational Circuits wk6Document15 pagesCombinational Circuits wk6Matthew LewisNo ratings yet

- Chapter 4 Combinational LogicDocument63 pagesChapter 4 Combinational Logicmdhuq1No ratings yet

- BIM203 - 07 - Arithmetic FunctionsDocument40 pagesBIM203 - 07 - Arithmetic Functionsayboaydo26No ratings yet

- Combinational Logic Circuit: University of Perpetual Help System DaltaDocument17 pagesCombinational Logic Circuit: University of Perpetual Help System DaltaJohn Kenneth BulabosNo ratings yet

- Arithmatic Circuit: S0 S1 Cin OutputsDocument3 pagesArithmatic Circuit: S0 S1 Cin Outputsapi-26551191No ratings yet

- Pimpri Chinchwad Education Trust's Pimpri Chinchwad College of Engineering Name-Vedant Dhote Roll No. - SYITA131 Assignment-3Document9 pagesPimpri Chinchwad Education Trust's Pimpri Chinchwad College of Engineering Name-Vedant Dhote Roll No. - SYITA131 Assignment-3Vedant DhoteNo ratings yet

- AdderDocument22 pagesAdderSHUBHAM KUMAR SINGHNo ratings yet

- BCSC 1201 Digital Logic and Electronic Circuits EXAM MSDocument7 pagesBCSC 1201 Digital Logic and Electronic Circuits EXAM MSndunguloren96No ratings yet

- شابتر4 الاولDocument64 pagesشابتر4 الاولمنار المالكيNo ratings yet

- 2exautkuuoDS - Exp - 3 - BCD ADDER - Roll No - 57 - Batch - 3Document6 pages2exautkuuoDS - Exp - 3 - BCD ADDER - Roll No - 57 - Batch - 3Manoj DohaleNo ratings yet

- Sistemas Digitales CompletaDocument144 pagesSistemas Digitales CompletaKarla DíazNo ratings yet

- Lecture 15 PDFDocument9 pagesLecture 15 PDFattiqueNo ratings yet

- Design The Following Combinatinal Logic CircuitDocument3 pagesDesign The Following Combinatinal Logic CircuitPEARL CAIRA MAE DIMALANTANo ratings yet

- Advanced VLSI Design: Dr. Premananda B.SDocument42 pagesAdvanced VLSI Design: Dr. Premananda B.SSmriti RaiNo ratings yet

- Carry Look Ahead AdderDocument14 pagesCarry Look Ahead Adderanony anonyNo ratings yet

- Lecture 2 BasicsDocument32 pagesLecture 2 Basicsmythemyaseen6No ratings yet

- Chap 06 Problem 02Document2 pagesChap 06 Problem 02ShahrukhNo ratings yet

- DLD Chapter 2Document49 pagesDLD Chapter 2Yenus KinduNo ratings yet

- 2s ComplemetDocument6 pages2s ComplemetRamisa NawarNo ratings yet

- 07 Pal Pla RomDocument26 pages07 Pal Pla RomAnamika PancholiNo ratings yet

- Lab 5 Binary ArithmeticDocument5 pagesLab 5 Binary ArithmeticIfthakharul Alam ShuvoNo ratings yet

- DLD Manual - EXP - 3Document3 pagesDLD Manual - EXP - 3Ahmad RazaNo ratings yet

- The Microoperations Most Often Encountered in Digital Computers Are Classified Into Four CategoriesDocument16 pagesThe Microoperations Most Often Encountered in Digital Computers Are Classified Into Four CategoriessouravNo ratings yet

- Bài tập chương 2, 3, 4Document7 pagesBài tập chương 2, 3, 4Phạm Hoàng DânNo ratings yet

- PH - Algorithm (New)Document2 pagesPH - Algorithm (New)mail.information0101No ratings yet

- Arithmetic Logic Unit (ALU) : Introduction To Computer P Yung-Yu ChuangDocument39 pagesArithmetic Logic Unit (ALU) : Introduction To Computer P Yung-Yu Chuangsifat islamNo ratings yet

- Rajni SH 19209121Document43 pagesRajni SH 19209121Rajnish KumarNo ratings yet

- Quiz 2 Elt-08Document4 pagesQuiz 2 Elt-08philbert khryss abadillaNo ratings yet

- Digital Logic Design: LectureDocument67 pagesDigital Logic Design: Lecturedream breakerNo ratings yet

- CAO Unit 1 - IIDocument23 pagesCAO Unit 1 - IIvbknukwcysgycpmlzsNo ratings yet

- Unit 1 QuestionsDocument15 pagesUnit 1 QuestionsLavanyaNo ratings yet

- Cse 205: Digital Logic DesignDocument89 pagesCse 205: Digital Logic DesignAfifa murshida NazinNo ratings yet

- COE211 CH3 BooleanMinimizationDocument26 pagesCOE211 CH3 BooleanMinimizationhm100hm100hm100No ratings yet

- Lab 1Document6 pagesLab 1faris.babiker.aliNo ratings yet

- Adc Lab 2-8-2017Document16 pagesAdc Lab 2-8-2017allanjwilsonNo ratings yet

- CA ArithmeticsDocument54 pagesCA ArithmeticsNguyễn Trương Trường AnNo ratings yet

- IT3030E CA Chap3 ArithmeticsDocument54 pagesIT3030E CA Chap3 Arithmeticshtdat181203No ratings yet

- Chapter 04Document33 pagesChapter 04Iqbal Ashfaq Joiya100% (1)

- Sistema II - Mathcad ImprimirDocument33 pagesSistema II - Mathcad ImprimirYhon W. Astopillo QuispeNo ratings yet

- Digital Computer Unit I Part5 (2022)Document20 pagesDigital Computer Unit I Part5 (2022)suhelkhan900500No ratings yet

- Unit1 - Lecture1 - Combinational Circuits - CSE211-13623-Anil RawatDocument21 pagesUnit1 - Lecture1 - Combinational Circuits - CSE211-13623-Anil RawatShanmukha GopuNo ratings yet

- National University of Computer and Emerging Sciences, Lahore CampusDocument2 pagesNational University of Computer and Emerging Sciences, Lahore CampusxxxNo ratings yet

- Microprocessor and Assembly Language: Lecture-2-Integer RepresentationDocument66 pagesMicroprocessor and Assembly Language: Lecture-2-Integer RepresentationAli SarmadNo ratings yet

- Unit1 P1JSPSinghDocument61 pagesUnit1 P1JSPSinghAryan RathoreNo ratings yet

- Multi SUbstractorDocument15 pagesMulti SUbstractorAdinda Irfa ChairunnisaNo ratings yet

- Verlogic3 Chapter3Document60 pagesVerlogic3 Chapter3tiến nam nguyễnNo ratings yet

- This File Generates The Graph of The Skin DepthDocument1 pageThis File Generates The Graph of The Skin Depthrktiwary256034No ratings yet

- This File Generates The Graph For Example 2Document1 pageThis File Generates The Graph For Example 2rktiwary256034No ratings yet

- This File Generates The Graph of The Current Density inDocument1 pageThis File Generates The Graph of The Current Density inrktiwary256034No ratings yet

- This File Generates The Graph For Example 3Document1 pageThis File Generates The Graph For Example 3rktiwary256034No ratings yet

- Subj:Digital Design: R K TiwaryDocument31 pagesSubj:Digital Design: R K Tiwaryrktiwary256034No ratings yet

- PMOS - Diode Connected LoadDocument1 pagePMOS - Diode Connected Loadrktiwary256034No ratings yet

- 2nd Lab Assignment - QuestionsDocument1 page2nd Lab Assignment - Questionsrktiwary256034No ratings yet

- Bits Pilani: Rktiwary Digital DesignDocument36 pagesBits Pilani: Rktiwary Digital Designrktiwary256034No ratings yet

- Subj:Digital Design: R K TiwaryDocument59 pagesSubj:Digital Design: R K Tiwaryrktiwary256034No ratings yet

- Bits Pilani: Digital Systems (Combinational Circuit) Rktiwary ManoDocument39 pagesBits Pilani: Digital Systems (Combinational Circuit) Rktiwary Manorktiwary256034No ratings yet

- Subj:Digital Design: R K TiwaryDocument40 pagesSubj:Digital Design: R K Tiwaryrktiwary256034No ratings yet

- DEM 2020 Midsem Makeup Answer Key Section ADocument3 pagesDEM 2020 Midsem Makeup Answer Key Section Arktiwary256034No ratings yet

- Birla Institute of Technology & Science, PilaniDocument7 pagesBirla Institute of Technology & Science, Pilanirktiwary256034No ratings yet

- Digital Electronics and Microprocessors Quiz 1: Answer: DDocument4 pagesDigital Electronics and Microprocessors Quiz 1: Answer: Drktiwary256034No ratings yet

- DEM 2020 Midsem Makeup Answer Key Section ADocument3 pagesDEM 2020 Midsem Makeup Answer Key Section Arktiwary256034No ratings yet

- Lab Exercise 7 - Barrel ShifterDocument2 pagesLab Exercise 7 - Barrel Shifterrktiwary256034No ratings yet

- Lab Exercise - 1 VLSI Design Latch ConfigurationDocument4 pagesLab Exercise - 1 VLSI Design Latch Configurationrktiwary256034No ratings yet

- Lab Exercise9 - CCMOSLatchDocument2 pagesLab Exercise9 - CCMOSLatchrktiwary256034No ratings yet

- Lab Exercise2 - Edge TriggeredDocument4 pagesLab Exercise2 - Edge Triggeredrktiwary256034No ratings yet

- Qos &flow CharacteristicsDocument16 pagesQos &flow CharacteristicsAbin JohnNo ratings yet

- A Definitive Guide To DFM Success Issue IDocument11 pagesA Definitive Guide To DFM Success Issue ISubodh KumarNo ratings yet

- Zoology Thesis HelpDocument7 pagesZoology Thesis Helpdnrz0g8y100% (1)

- Che Module 3aDocument127 pagesChe Module 3aPerter K MNo ratings yet

- Control System Lab 9Document10 pagesControl System Lab 9Niamatullah WazirNo ratings yet

- "Simple Rules of 4 Step Theory": Rule 1Document5 pages"Simple Rules of 4 Step Theory": Rule 1SaptarishisAstrology100% (2)

- Research2Module 3writing The SummaryDocument7 pagesResearch2Module 3writing The Summarynoresa comaraNo ratings yet

- Murphy ESP 100 PDFDocument2 pagesMurphy ESP 100 PDFRafael Antonio Triana PulidoNo ratings yet

- Systems Engineering: Designing, Implementing, Deploying and Operating Systems Which Include Hardware, Software and PeopleDocument47 pagesSystems Engineering: Designing, Implementing, Deploying and Operating Systems Which Include Hardware, Software and Peoplebilal ahmadNo ratings yet

- United States Patent (16) Patent N6. US 6,564,491 B2Document5 pagesUnited States Patent (16) Patent N6. US 6,564,491 B2edef345No ratings yet

- Error Codes - Roland - XJ740Document2 pagesError Codes - Roland - XJ740DimaNo ratings yet

- Temperature Control of CSTR Using PID Controller: Rubi, Vipul Agarwal, Anuj Deo, Nitin KumarDocument4 pagesTemperature Control of CSTR Using PID Controller: Rubi, Vipul Agarwal, Anuj Deo, Nitin KumarDiyar AliNo ratings yet

- Lecture Note On Crystal Structures Solid State Physics: June 2015Document62 pagesLecture Note On Crystal Structures Solid State Physics: June 2015Usama HafeezNo ratings yet

- FTR 900 Singular Cab y Crew Cab Australia PDFDocument4 pagesFTR 900 Singular Cab y Crew Cab Australia PDFdionymackNo ratings yet

- CI-US-01 en 1.5 UsersGuideDocument140 pagesCI-US-01 en 1.5 UsersGuideKerr PalaranNo ratings yet

- Achievers C1 Test Unit 2 ConsolidationDocument4 pagesAchievers C1 Test Unit 2 ConsolidationAlex GomezNo ratings yet

- Ex. Thread &tapDocument11 pagesEx. Thread &tapSebastianNo ratings yet

- Neutral Grounding Resistor (NGR)Document14 pagesNeutral Grounding Resistor (NGR)vennapusa VenkateshNo ratings yet

- LESSON-EXEMPLAR-DRRR (Module 9)Document3 pagesLESSON-EXEMPLAR-DRRR (Module 9)Unel Reynoso100% (2)

- Chapter 6Document21 pagesChapter 6Mazhar Hussain Ch.No ratings yet

- Introduction To Ops MGT-BSACF - (New)Document8 pagesIntroduction To Ops MGT-BSACF - (New)Hashim MughalNo ratings yet

- Foxconn G41mxe (Rev 1.0)Document34 pagesFoxconn G41mxe (Rev 1.0)alejandro correaNo ratings yet

- 860 KF Thermoprep: ManualDocument59 pages860 KF Thermoprep: ManualKarla CalderónNo ratings yet

- A Study On Product Packaging Impact On Consumer Buying BehaviourDocument9 pagesA Study On Product Packaging Impact On Consumer Buying BehaviourNovelty JournalsNo ratings yet