Professional Documents

Culture Documents

PHY 234 - Week Fourth - Lecture 2

PHY 234 - Week Fourth - Lecture 2

Uploaded by

Fatima Khan0 ratings0% found this document useful (0 votes)

6 views15 pagesThis document discusses different types of flip flops used in electronics. It describes the basic RS flip flop and how it works. It then discusses clocked or gated flip flops which only change state when a clock pulse is applied. Master-slave flip flops are described as using two flip flops to isolate input changes from multiple output changes during a single clock pulse. JK and T flip flops are also summarized as variations that address invalid states in RS flip flops. The document is presented by Dr. Muhammad Habib from COMSATS University Islamabad for the PHY 234 Electronics course in Spring 2021.

Original Description:

Original Title

PHY 234_Week Fourth _lecture 2

Copyright

© © All Rights Reserved

Available Formats

PPTX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThis document discusses different types of flip flops used in electronics. It describes the basic RS flip flop and how it works. It then discusses clocked or gated flip flops which only change state when a clock pulse is applied. Master-slave flip flops are described as using two flip flops to isolate input changes from multiple output changes during a single clock pulse. JK and T flip flops are also summarized as variations that address invalid states in RS flip flops. The document is presented by Dr. Muhammad Habib from COMSATS University Islamabad for the PHY 234 Electronics course in Spring 2021.

Copyright:

© All Rights Reserved

Available Formats

Download as PPTX, PDF, TXT or read online from Scribd

Download as pptx, pdf, or txt

0 ratings0% found this document useful (0 votes)

6 views15 pagesPHY 234 - Week Fourth - Lecture 2

PHY 234 - Week Fourth - Lecture 2

Uploaded by

Fatima KhanThis document discusses different types of flip flops used in electronics. It describes the basic RS flip flop and how it works. It then discusses clocked or gated flip flops which only change state when a clock pulse is applied. Master-slave flip flops are described as using two flip flops to isolate input changes from multiple output changes during a single clock pulse. JK and T flip flops are also summarized as variations that address invalid states in RS flip flops. The document is presented by Dr. Muhammad Habib from COMSATS University Islamabad for the PHY 234 Electronics course in Spring 2021.

Copyright:

© All Rights Reserved

Available Formats

Download as PPTX, PDF, TXT or read online from Scribd

Download as pptx, pdf, or txt

You are on page 1of 15

Electronics

PHY 234

Spring 2021

Dr. Muhammad Habib

Department of Physics

COMSATS University Islamabad

Applications of logic gates

RS flip flop or a latch

Clocked or gated flip flop

Master slave flip flop

JK flip flop

T flip flop

COMSATS University Islamabad 2

Applications of logic gates

Flip flop

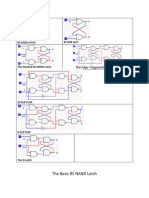

The basic flip-flop are also called binary or the R-S flip-flop (RSFF).

A flip-flop is a bistable device/circuit.

Both of its output states are stable.

The circuit remains in a particular output state indefinitely until something is done to change the output

conditions.

The circuit has

It has two inputs named S and R (which stand for Set and Reset)

and outputs labeled Q and .

Outputs (Q & ) of two NAND gates are feed back to the inputs of other gates.

COMSATS University Islamabad 3

Applications of logic gates

The four possible cases are summarized in the table.

Flip flop working can be started with both R and S high and Q and

in one of the two stable states.

Any change can be resume by making R or S low (logic 0).

In case 1, when Q, = 0, 1 initially, then making S low changes

the outputs to Q, = 1, 0.

Case 2 shows that if Q, = 1, 0 initially, then making

S low has no effect.

Similarly, cases 3 and 4 show that making R low leaves the

outputs in the state Q, = 0, 1 regardless of the initial state.

It can be summarized as the current output state tells us

which input was low last. If S was low last, then the output state will be

Q, = 1, 0. If R was low last, the output state will be Q, = 0, 1.

COMSATS University Islamabad 4

Flip flop types

• There are a few other types of flip flops.

Clocked Flip flop

This circuit is called the clocked or gated R-S flip-flop.

Its main part consist of a simple RS flip flop.

Another segment of two NAND gates is connected to the inputs of RS flip flop.

Now the state are controlled and only changes when there will be a low input to change states.

COMSATS University Islamabad 5

Clocked/ gated/ Synchronous S–R flip-flop

It is easy to change the output at certain instant of time.

The output will only change when there will be a clock pulse signal along with RS input.

The output will not change when the clock pulse is 0.

When the output changes state with the positive edge of the pulse, it is

positive-triggered clock and when the output changes state with

the negative edge of the pulse, it is negative clock.

Equivalent circuit

COMSATS University Islamabad 6

RS flip flop or a latch using NOR gates

COMSATS University Islamabad 7

Flip flop types

Master-Slave flip flop

A master-slave flip flop can be constructed with two separate flip flops

in which one will call master while other would serve as slave flip flop.

We have mentioned earlier that output of flip flop will change

only when there would be a clock pulse at input.

If there are multiple changes in the levels of the input/s S & R

during the time C is high, the outputs will also change multiple times.

The process of isolating input changes from multiple output changes

during a single input clock signal, so that the state of the inputs S and R

at one instant of time will be read and saved, is done by constructing a Master-Slave flip flop.

COMSATS University Islamabad 8

Flip flop types

Master-Slave flip flop

A master-slave flip flop can be constructed with two separate flip flops

in which one will call master while other would serve as slave flip flop.

We have mentioned earlier that output of flip flop will change

only when there would be a clock pulse at input.

If there are multiple changes in the levels of the input/s S & R

during the time C is high, the outputs will also change multiple times.

The process of isolating input changes from multiple output changes

during a single input clock signal, so that the state of the inputs S and R

at one instant of time will be read and saved, is done by constructing a Master-Slave flip flop.

Master-slave flip flop can be constructed with the NOR gates.

COMSATS University Islamabad 9

Master-Slave flip flop

Working of a master-slave flip flop

COMSATS University Islamabad 10

Additional information

COMSATS University Islamabad 11

Flip flop types

Simple RS flip flop exhibits

JK flip flop Invalid state with low inputs

Why do we need to make JK flip flop ?

If both inputs of Master-slave are High (logic 1) or

Low (logic 0) for RS flip flop then there will be

invalid or unpredictable state.

COMSATS University Islamabad 12

Flip flop types

JK (Jack Kilby) flip flop

Why do we need to make JK flip flop ?

If both inputs of Master-slave are High (logic 1) or

Low (logic 0) for RS flip flop then there will be

invalid or unpredictable state.

One way to deal with this problem is to add

feedback lines from the both outputs to the inputs.

A clocked flip flop with such kind of feedback formation

is called a JK flip flop and its inputs are renamed from

R S to J K.

COMSATS University Islamabad 13

Flip flop types

T flip flop

T flip flop is a single input version of the JK flip flop.

If both inputs (J & K) of the JK flip flop are tied together then T flip flop is formed.

Input T denotes toggling.

Whatever the state is present at the output, T flip flop will complement

it's output when T input is high (logic 1) along with the clock pulse.

In other word T flip flop inverts its outputs whenever

T input is triggered.

COMSATS University Islamabad 14

Thanks for your attention please.

COMSATS University Islamabad 15

You might also like

- Elements of Radio Servicing-William MarcusDocument368 pagesElements of Radio Servicing-William MarcusJShearerNo ratings yet

- Method of Statement Grounding System & Lightning ProtectionDocument7 pagesMethod of Statement Grounding System & Lightning Protectionafm0% (1)

- Accuvar PDFDocument4 pagesAccuvar PDFbmsingh100% (1)

- 3.flip FlopDocument19 pages3.flip FlopljjbNo ratings yet

- Flip-Flop Introduction To SR Flip FlopDocument22 pagesFlip-Flop Introduction To SR Flip FlopljjbNo ratings yet

- Chapter 2.2Document15 pagesChapter 2.2OzzyNo ratings yet

- Integrator Comparater Etc and OthersDocument4 pagesIntegrator Comparater Etc and Othersshaik jilanNo ratings yet

- Unit 5 Sequential CircuitDocument21 pagesUnit 5 Sequential CircuitAnurag GoelNo ratings yet

- Sharvin SR FlipDocument11 pagesSharvin SR FlipJohanNo ratings yet

- Flipflop NotesDocument19 pagesFlipflop NotesrmangaiNo ratings yet

- Dic Assignment Latches and Flip FlopsDocument6 pagesDic Assignment Latches and Flip FlopsMisha WaseemNo ratings yet

- Chap 8Document8 pagesChap 8mailusman9835No ratings yet

- Flip FlopsDocument11 pagesFlip FlopsZakaria JubarnNo ratings yet

- Flip FlopDocument34 pagesFlip Flopqwrr rewqNo ratings yet

- Unit-1 - FLIP FLOP - CODocument9 pagesUnit-1 - FLIP FLOP - COManesh PatelNo ratings yet

- Physics Laboratory Report: Experiment#4Document14 pagesPhysics Laboratory Report: Experiment#4M Salman RyanNo ratings yet

- Flip FlopsDocument3 pagesFlip FlopsnikomuzNo ratings yet

- The JK FlipDocument4 pagesThe JK Flipraj2510No ratings yet

- Sequential Digital Circuits: Flip FlopsDocument27 pagesSequential Digital Circuits: Flip FlopsSubrahmanyam GuduruNo ratings yet

- Flip-Flops (Bistables)Document11 pagesFlip-Flops (Bistables)Robert ChristianNo ratings yet

- Flip Flop Counters PDFDocument15 pagesFlip Flop Counters PDFAdarsh SinghNo ratings yet

- Flip Flops in Sequential CircuitsDocument9 pagesFlip Flops in Sequential Circuitsarpanrin2No ratings yet

- University of Gondar Institute of TechnologyDocument50 pagesUniversity of Gondar Institute of TechnologyamareNo ratings yet

- Unit 4Document11 pagesUnit 4anithar2No ratings yet

- Sequential CircuitsDocument134 pagesSequential CircuitsRajat KumarNo ratings yet

- Conversion of FlipDocument13 pagesConversion of FlipJohn Brix BalisterosNo ratings yet

- Project ReportDocument11 pagesProject Reportamiethurgat100% (2)

- BistabileDocument11 pagesBistabileRazvan IonutNo ratings yet

- Practical: 14 To Study J - K Flip Flop: Sohil Vohra (Lecturer - Shri K.J. Polytechnic College, Bharuch (C.E. Deptt) )Document5 pagesPractical: 14 To Study J - K Flip Flop: Sohil Vohra (Lecturer - Shri K.J. Polytechnic College, Bharuch (C.E. Deptt) )Sohil VohraNo ratings yet

- Flip Flop Play HokeyDocument7 pagesFlip Flop Play HokeyCherryPratamaNo ratings yet

- The J-K Flip Flop: ObjectivesDocument2 pagesThe J-K Flip Flop: ObjectivesALviNo ratings yet

- Flip FlopsDocument7 pagesFlip FlopsFord StephenNo ratings yet

- Unit-3-Sequential Logic Circuits-Static and Dynamic Latches ®istersDocument4 pagesUnit-3-Sequential Logic Circuits-Static and Dynamic Latches ®istersManimegalaiNo ratings yet

- What Is The Difference Between Latch and Flip FlopDocument12 pagesWhat Is The Difference Between Latch and Flip FlopJOYCENo ratings yet

- EEE 307 Logic CircuitsDocument16 pagesEEE 307 Logic Circuitsercan952No ratings yet

- Latches and Flip Flops PDFDocument19 pagesLatches and Flip Flops PDFTaran ShahNo ratings yet

- Date: 06-10-2020, 8AM-9 AM Branch: CS/2 Year Topic: Flip FlopsDocument14 pagesDate: 06-10-2020, 8AM-9 AM Branch: CS/2 Year Topic: Flip FlopsTech guru MaheshwariNo ratings yet

- Latches and Flip FlopsDocument13 pagesLatches and Flip FlopsM. Rayyan DawoodNo ratings yet

- Expt 12Document5 pagesExpt 12Dhrrishith VikalNo ratings yet

- Unit-1 - Digital ElectronicsDocument50 pagesUnit-1 - Digital ElectronicsVignesh VigneshNo ratings yet

- Izak Nel 209 324 067 DIT101T JK Flip-FlopDocument10 pagesIzak Nel 209 324 067 DIT101T JK Flip-FlopZack NelNo ratings yet

- Basics and Overview of Flip FlopsDocument5 pagesBasics and Overview of Flip FlopsMariaNo ratings yet

- JK Flip Flop Is The Most Widely Used of All The Flip-Flop Designs and Is ConsideredDocument1 pageJK Flip Flop Is The Most Widely Used of All The Flip-Flop Designs and Is ConsidereddbircsNo ratings yet

- The J K Flip FlopDocument3 pagesThe J K Flip FlopSaanguNo ratings yet

- Unit 4Document98 pagesUnit 4Shinigami DandyNo ratings yet

- Flip FlopDocument32 pagesFlip FlopAnoop KumarNo ratings yet

- Digital Logic Design Sequential LogicDocument31 pagesDigital Logic Design Sequential LogicsfdNo ratings yet

- 2 FlipflopDocument19 pages2 FlipfloplidhisijuNo ratings yet

- DL CH 4Document50 pagesDL CH 4Praches AcharyaNo ratings yet

- PHY 234 - Week 5th - Lecture 2Document10 pagesPHY 234 - Week 5th - Lecture 2Fatima KhanNo ratings yet

- Title ObjectiveDocument4 pagesTitle ObjectiveShekhar ShuklaNo ratings yet

- Lec # 06 - DLDDocument30 pagesLec # 06 - DLDSunny 17No ratings yet

- DSD Module 5Document81 pagesDSD Module 5Abinesh RNo ratings yet

- Sequential Logic Design LabDocument24 pagesSequential Logic Design LabLincoln MutangaNo ratings yet

- M7 Sequentials Circuits-1Document67 pagesM7 Sequentials Circuits-1joelNo ratings yet

- Engg BasicsDocument10 pagesEngg BasicsGnrajesh RajeshNo ratings yet

- DLD Chapter 6Document31 pagesDLD Chapter 6kalshkinguNo ratings yet

- Report 1 (D2, Digital)Document10 pagesReport 1 (D2, Digital)Kian YingNo ratings yet

- The Basic JK Flip-FlopDocument4 pagesThe Basic JK Flip-Flopom1444100% (1)

- Mod 5 - FLIPFLOPS and Its TypesDocument28 pagesMod 5 - FLIPFLOPS and Its TypesRavi CharanNo ratings yet

- Expt No.9Document5 pagesExpt No.9Rithika 318030No ratings yet

- PHY 234 - Week 7th - Lecture 2 - BJTDocument22 pagesPHY 234 - Week 7th - Lecture 2 - BJTFatima KhanNo ratings yet

- PHY 234 - Week 8th - Lecture - Adder-SubtractorDocument12 pagesPHY 234 - Week 8th - Lecture - Adder-SubtractorFatima KhanNo ratings yet

- PHY 234 - Week 5th - Lecture 2Document10 pagesPHY 234 - Week 5th - Lecture 2Fatima KhanNo ratings yet

- PHY 234 - First Week - Lecture 2Document13 pagesPHY 234 - First Week - Lecture 2Fatima KhanNo ratings yet

- PHY 234 - Second Week - Lecture 1Document10 pagesPHY 234 - Second Week - Lecture 1Fatima KhanNo ratings yet

- PHY 234 - First Week - Lecture 3Document9 pagesPHY 234 - First Week - Lecture 3Fatima KhanNo ratings yet

- PHY 234 - Second Week - Lecture 2 - RectifiersDocument10 pagesPHY 234 - Second Week - Lecture 2 - RectifiersFatima KhanNo ratings yet

- HeartviewDocument2 pagesHeartviewIsrael ExporterNo ratings yet

- Datasheet PMC-24V050W1AADocument12 pagesDatasheet PMC-24V050W1AARulo Hdez LazoNo ratings yet

- Diagrama Electrico de Transmcion 160HDocument4 pagesDiagrama Electrico de Transmcion 160HJuan CarlosNo ratings yet

- Dynalite Installers Course Training GuideDocument86 pagesDynalite Installers Course Training GuideAdi SeleaNo ratings yet

- Elmes CH4H Manual 05 - 2009 - php2BA46aDocument2 pagesElmes CH4H Manual 05 - 2009 - php2BA46aflorinNo ratings yet

- PDFDocument110 pagesPDFFrendz ExportNo ratings yet

- RRB Junior Electronics Engineer Study Material 3Document66 pagesRRB Junior Electronics Engineer Study Material 3thirumalNo ratings yet

- Aluminium Busbar Sizing Software OutputDocument3 pagesAluminium Busbar Sizing Software Outputkapil100% (4)

- Low Voltage General Purpose Motors: Brake Motor SectionDocument38 pagesLow Voltage General Purpose Motors: Brake Motor SectionsihamuNo ratings yet

- Research Paper On Bandpass FilterDocument6 pagesResearch Paper On Bandpass Filterfvesdf9j100% (1)

- Welbee English Web PDFDocument10 pagesWelbee English Web PDFekopujiantoeNo ratings yet

- North-West Switches and SocketsDocument4 pagesNorth-West Switches and SocketsambrosialnectarNo ratings yet

- Simulation About Battery Equalization Charging Based On The Fuzzy ControlDocument2 pagesSimulation About Battery Equalization Charging Based On The Fuzzy ControlBogovicNo ratings yet

- LM7812Document6 pagesLM7812Nguyễn Thanh QuangNo ratings yet

- ESC Manual Setting Options (Including Power Straight Version) 50A/60A/70A/80A/100A/125A/200ADocument4 pagesESC Manual Setting Options (Including Power Straight Version) 50A/60A/70A/80A/100A/125A/200APizda MaterinaNo ratings yet

- SUMMATIVE Test 2Document2 pagesSUMMATIVE Test 2Argesil SaysonNo ratings yet

- Introduction To Electronic Communications System: Main PurposeDocument65 pagesIntroduction To Electronic Communications System: Main PurposeMiguel VillarroelNo ratings yet

- Intelligence Power and Personality 1000812749 PDFDocument357 pagesIntelligence Power and Personality 1000812749 PDFImalis Epidaurus100% (1)

- SVCDocument92 pagesSVCDiego MaldonadoNo ratings yet

- Communication Theory Question Bank Unit 4Document2 pagesCommunication Theory Question Bank Unit 4muthubeNo ratings yet

- Discontinuous PWM Techniques For Open-End Winding Induction Motor Drive For Zero Sequence Voltage EliminationDocument13 pagesDiscontinuous PWM Techniques For Open-End Winding Induction Motor Drive For Zero Sequence Voltage EliminationarunkmepesNo ratings yet

- TBW PresentationDocument13 pagesTBW Presentationسیدہ ماریہNo ratings yet

- TPS8804 Smoke Detector AFE: 1 Features 2 ApplicationsDocument57 pagesTPS8804 Smoke Detector AFE: 1 Features 2 ApplicationsmotaNo ratings yet

- Standard Electrical SpecificationDocument9 pagesStandard Electrical SpecificationmatshonaNo ratings yet

- Victoria University: Lab Report To Investigate The Ferranti Effect Using Artificial Transmission LineDocument20 pagesVictoria University: Lab Report To Investigate The Ferranti Effect Using Artificial Transmission LineAyaz Ahmad100% (1)

- 141584Document3 pages141584Jose Luis RattiaNo ratings yet

- Operation Manual &: Strapping MachineDocument121 pagesOperation Manual &: Strapping Machinesamah yahiaNo ratings yet