Professional Documents

Culture Documents

0 ratings0% found this document useful (0 votes)

47 viewsMicroprocessor Without Interlocked Pipelined Stages

Microprocessor Without Interlocked Pipelined Stages

Uploaded by

Rifah TasniaThe document discusses the MIPS (Microprocessor without Interlocked Pipelined Stages) architecture. MIPS is a RISC instruction set architecture that uses a load-store design where only load and store instructions can access memory. It has 32 general-purpose registers and separate registers for floating point instructions. Memory is organized as a 1D array with byte addressing. MIPS instructions include data operations, data transfers, and sequencing instructions. There are three main instruction formats that lay out fields in a consistent way.

Copyright:

© All Rights Reserved

Available Formats

Download as PPTX, PDF, TXT or read online from Scribd

You might also like

- M.Sc. Course in Microprocessor DesignDocument43 pagesM.Sc. Course in Microprocessor Designحذيفة عامرNo ratings yet

- CA InstructionSet HoDocument15 pagesCA InstructionSet HoNobin MathewNo ratings yet

- ISA - CISC VS RISC - Intro To MIPSDocument59 pagesISA - CISC VS RISC - Intro To MIPSAffan GhazaliNo ratings yet

- Week 3 - IsA Appendix A Sp24Document48 pagesWeek 3 - IsA Appendix A Sp24FA20-BCS-077 (SUFIYAN CHISHTY) UnknownNo ratings yet

- 1062 PDFDocument84 pages1062 PDFPrachi OberaiNo ratings yet

- Fundamentals of MicroprocessorDocument43 pagesFundamentals of MicroprocessorPrajaktaNo ratings yet

- 01 Risc MF PDFDocument123 pages01 Risc MF PDFmohmmad omarNo ratings yet

- 1 Introduction To Computers and Computer OrganizationDocument36 pages1 Introduction To Computers and Computer Organizationemansheraz7No ratings yet

- 1 - Introduction To Computers and Computer OrganizationDocument35 pages1 - Introduction To Computers and Computer OrganizationHammad UllahNo ratings yet

- Mips IsaDocument19 pagesMips IsaHritwik GhoshNo ratings yet

- Microprocessor IntroductionDocument29 pagesMicroprocessor IntroductionvshlvvkNo ratings yet

- Intro To ARM Cortex-M3 (CM3) and LPC17xx MCU: OutlineDocument79 pagesIntro To ARM Cortex-M3 (CM3) and LPC17xx MCU: OutlinesupriyaNo ratings yet

- CSE 259 Lecture4Document14 pagesCSE 259 Lecture4robin haqueNo ratings yet

- 2 NdmicroDocument20 pages2 Ndmicroaklilu YebuzeyeNo ratings yet

- Lecture OneDocument36 pagesLecture OneMworozi DicksonNo ratings yet

- CO Assignment-1: ISA With Reference To MIPSDocument3 pagesCO Assignment-1: ISA With Reference To MIPSMANAS AGARWALNo ratings yet

- Lec02 The Microprocessor and Its ArchitectureDocument39 pagesLec02 The Microprocessor and Its ArchitectureAmr Ahmed GomaaNo ratings yet

- Week 10 2021Document42 pagesWeek 10 2021ngokfong yuNo ratings yet

- Lecture#2 Fut Microprocessor PDFDocument81 pagesLecture#2 Fut Microprocessor PDFAhmedGamalNo ratings yet

- Microprocessor 8085Document341 pagesMicroprocessor 8085nikhil singhNo ratings yet

- Assgnment 2 ArchitectureDocument3 pagesAssgnment 2 ArchitecturebasiledembeNo ratings yet

- Internal Organization of A PC: MemoryDocument33 pagesInternal Organization of A PC: MemoryPrasath SanthanamNo ratings yet

- System Software Unit IDocument39 pagesSystem Software Unit IRaja GsNo ratings yet

- Microprocessors & InterfacingDocument255 pagesMicroprocessors & InterfacingSasi BhushanNo ratings yet

- Uvod Do Mikroprocesorove TechnikyDocument132 pagesUvod Do Mikroprocesorove TechnikyVrushabh SahareNo ratings yet

- 4.13 A Discussion On DecodingDocument12 pages4.13 A Discussion On DecodingyfiamataimNo ratings yet

- Lec 2-Intel x86 Processor Architecture and EvolutionDocument37 pagesLec 2-Intel x86 Processor Architecture and EvolutionIsaac SindigaNo ratings yet

- 6 Mips DatapathDocument55 pages6 Mips Datapath1352 : NEEBESH PADHYNo ratings yet

- Advanced Risc MachinersDocument21 pagesAdvanced Risc MachinersAANCHALNo ratings yet

- Introduction To RISC Processor: Ni Logic Pvt. LTD., PuneDocument42 pagesIntroduction To RISC Processor: Ni Logic Pvt. LTD., PuneAnil Kumar KadiyalaNo ratings yet

- Lecture 5 Digital Computing SystemsDocument30 pagesLecture 5 Digital Computing SystemsSRA893No ratings yet

- MPS Lecture 3 - The Microprocessor and Its ArchitectureDocument26 pagesMPS Lecture 3 - The Microprocessor and Its ArchitectureShehroze TalatNo ratings yet

- Lec 5 Flip Flop &latches and GlitchesDocument55 pagesLec 5 Flip Flop &latches and GlitchesSadia KhanNo ratings yet

- Amp Units 3&4 NotesDocument18 pagesAmp Units 3&4 NotesSumithNo ratings yet

- Ece4750 T01 Proc ScycleDocument24 pagesEce4750 T01 Proc ScyclekartimidNo ratings yet

- Microprocessor I - Lecture 02Document45 pagesMicroprocessor I - Lecture 02Omar Mohamed Farag Abd El FattahNo ratings yet

- Single-Cycle MIPS ProcessorDocument15 pagesSingle-Cycle MIPS ProcessorMALIK AWAIS UR REHMANNo ratings yet

- Basic Operational ConceptsDocument31 pagesBasic Operational Conceptsdeepakbinoy51No ratings yet

- Chapter 2 AssemblyDocument55 pagesChapter 2 AssemblySolomon SBNo ratings yet

- 8086 Microprocessor ArchitectureDocument132 pages8086 Microprocessor ArchitectureSai Krishna KodaliNo ratings yet

- Nios II IntroductionDocument91 pagesNios II IntroductionRajan VermaNo ratings yet

- 1 IntroductionDocument40 pages1 Introduction3sfr3sfrNo ratings yet

- Computer Architecture TaxonomyDocument13 pagesComputer Architecture TaxonomySuresh VaruvelNo ratings yet

- LM03 - Lesson 5 Fundamentals of Microprocessor 2Document26 pagesLM03 - Lesson 5 Fundamentals of Microprocessor 2Norman Jay GarciaNo ratings yet

- Gecassets - Co.in - 8085 Microprocessor - Ramesh GaonkarDocument330 pagesGecassets - Co.in - 8085 Microprocessor - Ramesh Gaonkargannoju423No ratings yet

- Microprocessor: Evolution & Insights of 8086Document43 pagesMicroprocessor: Evolution & Insights of 8086நட்ராஜ் நாதன்No ratings yet

- MP Unit 1 OneshotDocument8 pagesMP Unit 1 Oneshotlococo2836No ratings yet

- 16 Bit RISC ProcessorDocument4 pages16 Bit RISC ProcessorTanvir AhmadNo ratings yet

- SIMD PresentationDocument28 pagesSIMD PresentationHuzaifaNo ratings yet

- Embedded ProcessorsDocument7 pagesEmbedded ProcessorsVinod ShaivaNo ratings yet

- 01 Introduction To MicroprocessorDocument57 pages01 Introduction To MicroprocessorMuhammad JunaidNo ratings yet

- ARM - Advanced RISC Machines: RISC-Reduce Instruction Set ComputersDocument60 pagesARM - Advanced RISC Machines: RISC-Reduce Instruction Set ComputersPraveen EdulaNo ratings yet

- Lecture 3Document24 pagesLecture 3Mohsin AliNo ratings yet

- Study of Architecture of DSP TMS320C6748Document9 pagesStudy of Architecture of DSP TMS320C6748Varssha BNo ratings yet

- Marie: An Introduction To A Simple ComputerDocument19 pagesMarie: An Introduction To A Simple ComputerRizwan AliNo ratings yet

- Computer Architecture Lecture Notes Spring 2005 Dr. Michael P. Frank Competency Area 3: Programming and Coding MethodsDocument68 pagesComputer Architecture Lecture Notes Spring 2005 Dr. Michael P. Frank Competency Area 3: Programming and Coding MethodsNapsterNo ratings yet

- MIPS Processor R3000: RegistersDocument76 pagesMIPS Processor R3000: Registersmalik Al kadahNo ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationFrom EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNo ratings yet

- Group 5Document72 pagesGroup 5Rifah TasniaNo ratings yet

- CH 8 StallingsDocument38 pagesCH 8 StallingsRifah TasniaNo ratings yet

- CH 8 StallingsDocument38 pagesCH 8 StallingsRifah TasniaNo ratings yet

- AssignmentDocument9 pagesAssignmentRifah TasniaNo ratings yet

Microprocessor Without Interlocked Pipelined Stages

Microprocessor Without Interlocked Pipelined Stages

Uploaded by

Rifah Tasnia0 ratings0% found this document useful (0 votes)

47 views9 pagesThe document discusses the MIPS (Microprocessor without Interlocked Pipelined Stages) architecture. MIPS is a RISC instruction set architecture that uses a load-store design where only load and store instructions can access memory. It has 32 general-purpose registers and separate registers for floating point instructions. Memory is organized as a 1D array with byte addressing. MIPS instructions include data operations, data transfers, and sequencing instructions. There are three main instruction formats that lay out fields in a consistent way.

Original Description:

Copyright

© © All Rights Reserved

Available Formats

PPTX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThe document discusses the MIPS (Microprocessor without Interlocked Pipelined Stages) architecture. MIPS is a RISC instruction set architecture that uses a load-store design where only load and store instructions can access memory. It has 32 general-purpose registers and separate registers for floating point instructions. Memory is organized as a 1D array with byte addressing. MIPS instructions include data operations, data transfers, and sequencing instructions. There are three main instruction formats that lay out fields in a consistent way.

Copyright:

© All Rights Reserved

Available Formats

Download as PPTX, PDF, TXT or read online from Scribd

Download as pptx, pdf, or txt

0 ratings0% found this document useful (0 votes)

47 views9 pagesMicroprocessor Without Interlocked Pipelined Stages

Microprocessor Without Interlocked Pipelined Stages

Uploaded by

Rifah TasniaThe document discusses the MIPS (Microprocessor without Interlocked Pipelined Stages) architecture. MIPS is a RISC instruction set architecture that uses a load-store design where only load and store instructions can access memory. It has 32 general-purpose registers and separate registers for floating point instructions. Memory is organized as a 1D array with byte addressing. MIPS instructions include data operations, data transfers, and sequencing instructions. There are three main instruction formats that lay out fields in a consistent way.

Copyright:

© All Rights Reserved

Available Formats

Download as PPTX, PDF, TXT or read online from Scribd

Download as pptx, pdf, or txt

You are on page 1of 9

Microprocessor without

Interlocked Pipelined Stages

(MIPS)

Introduction

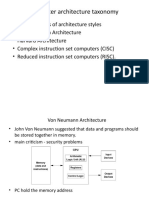

• It is a reduced instruction set computer (RISC) instruction set architecture (ISA).

• MIPS is a load-store architecture, which means that only load and store instructions

can access memory. All other instructions (add, sub, mul, div, and, or, etc.) must get

their operands from registers and store their results in a register.

• The first version of the MIPS architecture was designed by MIPS Computer

Systems for its R2000 microprocessor, the first MIPS implementation. Both MIPS

and the R2000 were introduced together in 1985.

• It contains:

1. Registers

2. Memory

3. Instructions

Registers

• The MIPS processor has 32 general-purpose registers, so it takes 5 bits to specify

which one to use.

• The MIPS processor has one standard register file containing 32 32-bit registers for

use by integer and logic instructions. These registers are called $0 through $31

• The MIPS processor has a separate register file for floating point instructions, which

contains another 32 32-bit registers called $f0 through $f31.

• A few special registers

-PC

-Hi & Lo results of multiplication

-Floating point registers

-Control registers (for errors and status)

MIPS Registers

Memory Organization

• Memory is a large 1-dimension array.

• Each location is one byte (8 bits).

• A memory address indexes into the array.

• For a 32-bit computer there are 2^32 memory locations (4GB).

• For a 64-bit computer there are 2^64 memory locations (16EB).

-64-bit ×86 machines tend to be limited to ~48-bits of address

space, or 4PB.

Memory Organization

MIPS Instructions

• Types of Instructions

1. Data Operations

-Arithmetic

-Logical

2. Data transfer

-Load

-Store

3. Sequencing

-Branch

-Jump

MIPS Instruction (cont.)

See MIPS_Instruction_Set.pdf

Instruction Formats

• There are 3 main instruction formats in MIPS. The fields in each type

are laid out in such a way that the same fields are always in the same

place for each type.

You might also like

- M.Sc. Course in Microprocessor DesignDocument43 pagesM.Sc. Course in Microprocessor Designحذيفة عامرNo ratings yet

- CA InstructionSet HoDocument15 pagesCA InstructionSet HoNobin MathewNo ratings yet

- ISA - CISC VS RISC - Intro To MIPSDocument59 pagesISA - CISC VS RISC - Intro To MIPSAffan GhazaliNo ratings yet

- Week 3 - IsA Appendix A Sp24Document48 pagesWeek 3 - IsA Appendix A Sp24FA20-BCS-077 (SUFIYAN CHISHTY) UnknownNo ratings yet

- 1062 PDFDocument84 pages1062 PDFPrachi OberaiNo ratings yet

- Fundamentals of MicroprocessorDocument43 pagesFundamentals of MicroprocessorPrajaktaNo ratings yet

- 01 Risc MF PDFDocument123 pages01 Risc MF PDFmohmmad omarNo ratings yet

- 1 Introduction To Computers and Computer OrganizationDocument36 pages1 Introduction To Computers and Computer Organizationemansheraz7No ratings yet

- 1 - Introduction To Computers and Computer OrganizationDocument35 pages1 - Introduction To Computers and Computer OrganizationHammad UllahNo ratings yet

- Mips IsaDocument19 pagesMips IsaHritwik GhoshNo ratings yet

- Microprocessor IntroductionDocument29 pagesMicroprocessor IntroductionvshlvvkNo ratings yet

- Intro To ARM Cortex-M3 (CM3) and LPC17xx MCU: OutlineDocument79 pagesIntro To ARM Cortex-M3 (CM3) and LPC17xx MCU: OutlinesupriyaNo ratings yet

- CSE 259 Lecture4Document14 pagesCSE 259 Lecture4robin haqueNo ratings yet

- 2 NdmicroDocument20 pages2 Ndmicroaklilu YebuzeyeNo ratings yet

- Lecture OneDocument36 pagesLecture OneMworozi DicksonNo ratings yet

- CO Assignment-1: ISA With Reference To MIPSDocument3 pagesCO Assignment-1: ISA With Reference To MIPSMANAS AGARWALNo ratings yet

- Lec02 The Microprocessor and Its ArchitectureDocument39 pagesLec02 The Microprocessor and Its ArchitectureAmr Ahmed GomaaNo ratings yet

- Week 10 2021Document42 pagesWeek 10 2021ngokfong yuNo ratings yet

- Lecture#2 Fut Microprocessor PDFDocument81 pagesLecture#2 Fut Microprocessor PDFAhmedGamalNo ratings yet

- Microprocessor 8085Document341 pagesMicroprocessor 8085nikhil singhNo ratings yet

- Assgnment 2 ArchitectureDocument3 pagesAssgnment 2 ArchitecturebasiledembeNo ratings yet

- Internal Organization of A PC: MemoryDocument33 pagesInternal Organization of A PC: MemoryPrasath SanthanamNo ratings yet

- System Software Unit IDocument39 pagesSystem Software Unit IRaja GsNo ratings yet

- Microprocessors & InterfacingDocument255 pagesMicroprocessors & InterfacingSasi BhushanNo ratings yet

- Uvod Do Mikroprocesorove TechnikyDocument132 pagesUvod Do Mikroprocesorove TechnikyVrushabh SahareNo ratings yet

- 4.13 A Discussion On DecodingDocument12 pages4.13 A Discussion On DecodingyfiamataimNo ratings yet

- Lec 2-Intel x86 Processor Architecture and EvolutionDocument37 pagesLec 2-Intel x86 Processor Architecture and EvolutionIsaac SindigaNo ratings yet

- 6 Mips DatapathDocument55 pages6 Mips Datapath1352 : NEEBESH PADHYNo ratings yet

- Advanced Risc MachinersDocument21 pagesAdvanced Risc MachinersAANCHALNo ratings yet

- Introduction To RISC Processor: Ni Logic Pvt. LTD., PuneDocument42 pagesIntroduction To RISC Processor: Ni Logic Pvt. LTD., PuneAnil Kumar KadiyalaNo ratings yet

- Lecture 5 Digital Computing SystemsDocument30 pagesLecture 5 Digital Computing SystemsSRA893No ratings yet

- MPS Lecture 3 - The Microprocessor and Its ArchitectureDocument26 pagesMPS Lecture 3 - The Microprocessor and Its ArchitectureShehroze TalatNo ratings yet

- Lec 5 Flip Flop &latches and GlitchesDocument55 pagesLec 5 Flip Flop &latches and GlitchesSadia KhanNo ratings yet

- Amp Units 3&4 NotesDocument18 pagesAmp Units 3&4 NotesSumithNo ratings yet

- Ece4750 T01 Proc ScycleDocument24 pagesEce4750 T01 Proc ScyclekartimidNo ratings yet

- Microprocessor I - Lecture 02Document45 pagesMicroprocessor I - Lecture 02Omar Mohamed Farag Abd El FattahNo ratings yet

- Single-Cycle MIPS ProcessorDocument15 pagesSingle-Cycle MIPS ProcessorMALIK AWAIS UR REHMANNo ratings yet

- Basic Operational ConceptsDocument31 pagesBasic Operational Conceptsdeepakbinoy51No ratings yet

- Chapter 2 AssemblyDocument55 pagesChapter 2 AssemblySolomon SBNo ratings yet

- 8086 Microprocessor ArchitectureDocument132 pages8086 Microprocessor ArchitectureSai Krishna KodaliNo ratings yet

- Nios II IntroductionDocument91 pagesNios II IntroductionRajan VermaNo ratings yet

- 1 IntroductionDocument40 pages1 Introduction3sfr3sfrNo ratings yet

- Computer Architecture TaxonomyDocument13 pagesComputer Architecture TaxonomySuresh VaruvelNo ratings yet

- LM03 - Lesson 5 Fundamentals of Microprocessor 2Document26 pagesLM03 - Lesson 5 Fundamentals of Microprocessor 2Norman Jay GarciaNo ratings yet

- Gecassets - Co.in - 8085 Microprocessor - Ramesh GaonkarDocument330 pagesGecassets - Co.in - 8085 Microprocessor - Ramesh Gaonkargannoju423No ratings yet

- Microprocessor: Evolution & Insights of 8086Document43 pagesMicroprocessor: Evolution & Insights of 8086நட்ராஜ் நாதன்No ratings yet

- MP Unit 1 OneshotDocument8 pagesMP Unit 1 Oneshotlococo2836No ratings yet

- 16 Bit RISC ProcessorDocument4 pages16 Bit RISC ProcessorTanvir AhmadNo ratings yet

- SIMD PresentationDocument28 pagesSIMD PresentationHuzaifaNo ratings yet

- Embedded ProcessorsDocument7 pagesEmbedded ProcessorsVinod ShaivaNo ratings yet

- 01 Introduction To MicroprocessorDocument57 pages01 Introduction To MicroprocessorMuhammad JunaidNo ratings yet

- ARM - Advanced RISC Machines: RISC-Reduce Instruction Set ComputersDocument60 pagesARM - Advanced RISC Machines: RISC-Reduce Instruction Set ComputersPraveen EdulaNo ratings yet

- Lecture 3Document24 pagesLecture 3Mohsin AliNo ratings yet

- Study of Architecture of DSP TMS320C6748Document9 pagesStudy of Architecture of DSP TMS320C6748Varssha BNo ratings yet

- Marie: An Introduction To A Simple ComputerDocument19 pagesMarie: An Introduction To A Simple ComputerRizwan AliNo ratings yet

- Computer Architecture Lecture Notes Spring 2005 Dr. Michael P. Frank Competency Area 3: Programming and Coding MethodsDocument68 pagesComputer Architecture Lecture Notes Spring 2005 Dr. Michael P. Frank Competency Area 3: Programming and Coding MethodsNapsterNo ratings yet

- MIPS Processor R3000: RegistersDocument76 pagesMIPS Processor R3000: Registersmalik Al kadahNo ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationFrom EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNo ratings yet

- Group 5Document72 pagesGroup 5Rifah TasniaNo ratings yet

- CH 8 StallingsDocument38 pagesCH 8 StallingsRifah TasniaNo ratings yet

- CH 8 StallingsDocument38 pagesCH 8 StallingsRifah TasniaNo ratings yet

- AssignmentDocument9 pagesAssignmentRifah TasniaNo ratings yet