Professional Documents

Culture Documents

Central Processing Unit

Central Processing Unit

Uploaded by

kuripunjabi066Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Central Processing Unit

Central Processing Unit

Uploaded by

kuripunjabi066Copyright:

Available Formats

Central Processing Unit 1

CENTRAL PROCESSING UNIT

1. Introduction

2. General Register Organization

3. Stack Organization

4. Instruction Formats

5. Addressing Modes

6. Data Transfer and Manipulation

Instructions

7. Reduced Instruction Set Computer

8. Complex Instruction set

Computer Organization Prof. H. Yoon

Central Processing Unit 2

Introduction

• The part of the computer that performs the bulk of data

processing operations is called central processing unit.

• CPU is based on major three parts

1. Register set (stored intermediate data during the

execution of instructions)

2. ALU (performs the required micro and arithmetic

operations)

3. Control Unit (supervise the transfer of information

among the registers and ALU)

Computer Organization Prof. H. Yoon

Central Processing Unit 3 Introduction

MAJOR COMPONENTS OF CPU

• Storage Components

Registers

Flags

• Execution (Processing) Components

Arithmetic Logic Unit (ALU)

Arithmetic calculations, Logical computations, Shifts/Rotates

• Transfer Components

Bus

• Control Components

Register

Control Unit ALU

Control Unit

Computer Organization Prof. H. Yoon

Central Processing Unit 4

REGISTERS

In Basic Computer, there is only one general purpose register,

the Accumulator (AC)

In modern CPUs, there are many general purpose registers

It is advantageous to have many registers

– Transfer between registers within the processor are relatively fast

– Going “off the processor” to access memory is much slower

Computer Organization Prof. H. Yoon

Central Processing Unit 5

General Register Organization

Generally CPU has seven general registers. Register

organization show how registers are selected and how data

flow between register and ALU

When we are using multiple general-purpose registers, instead

of a single accumulator register, in the CPU Organization then

this type of organization is known as General register-based

CPU Organization

Computer Organization Prof. H. Yoon

Central Processing Unit 6 General Register Organization

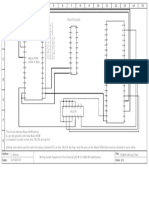

GENERAL REGISTER ORGANIZATION

Input

Clock

R1

R2

R3

R4

R5

R6

R7

Load

(7 lines)

SELA { MUX MUX } SELB

3x8

A bus B bus

decoder

SELD

OPR ALU

Output

Computer Organization Prof. H. Yoon

Central Processing Unit 7 Control

OPERATION OF CONTROL UNIT

The control unit

Directs the information flow through ALU by

- Selecting various Components in the system

- Selecting the Function of ALU

Example: R1 R2 + R3 R4⟵ R4.R5

[1] MUX A selector (SELA): BUS A R2

[2] MUX B selector (SELB): BUS B R3

[3] ALU operation selector (OPR): ALU to ADD

[4] Decoder destination selector (SELD): R1 Out Bus

3 3 3 5

Control Word SELA SELB SELD OPR

Encoding of register selection fields

Binary

Code SELA SELB SELD

000 Input Input None

001 R1 R1 R1

010 R2 R2 R2

011 R3 R3 R3

100 R4 R4 R4

101 R5 R5 R5

110 R6 R6 R6

111 R7 R7 R7

Computer Organization Prof. H. Yoon

Central Processing Unit 8 Control

ALU CONTROL

Encoding of ALU operations OPR

Select Operation Symbol

00000 Transfer A TSFA

00001 Increment A INCA

00010 ADD A + B ADD

00101 Subtract A - B SUB

00110 Decrement A DECA

01000 AND A and B AND

01010 OR A and B OR

01100 XOR A and B XOR

01110 Complement A COMA

10000 Shift right A SHRA

11000 Shift left A SHLA

Examples of ALU Microoperations

Symbolic Designation

Microoperation SELA SELB SELD OPR Control Word

R1 R2 R3 R2 R3 R1 SUB 010 011 001 00101

R4 R4 R5 R4 R5 R4 OR 100 101 100 01010

R6 R6 + 1 R6 - R6 INCA 110 000 110 00001

R7 R1 R1 - R7 TSFA 001 000 111 00000

Output R2 R2 - None TSFA 010 000 000 00000

Output Input Input - None TSFA 000 000 000 00000

R4 shl R4 R4 - R4 SHLA 100 000 100 11000

R5 0 R5 R5 R5 XOR 101 101 101 01100

Computer Organization Prof. H. Yoon

Central Processing Unit 9

Stack organization

• Stack is a storage structure that stores information in

such a way that the last item stored is the first item

retrieved.

• It is based on the principle of LIFO (Last-in-first-out). The

stack in digital computers is a group of memory locations

with a register that holds the address of top of element.

• There are two types of stack organization which are used

in the computer hardware. - It is built using register

• Memory stack

• Register stack

Computer Organization Prof. H. Yoon

Central Processing Unit 10 Stack Organization

REGISTER STACK ORGANIZATION

Stack

- efficient for arithmetic expression evaluation

- Storage which can be accessed in LIFO

- Pointer: SP

- Only PUSH and POP operations are applicable

stack Address

Register Stack Flags 63

FULL EMPTY

Stack pointer 4

SP C 3

6 bits B 2

A 1

Push, Pop operations 0

DR

Initially, SP = 0, EMPTY = 1, FULL = 0

PUSH POP

SP SP + 1 DR M[SP]

M[SP] DR SP SP 1

If (SP = 0) then (FULL 1) If (SP = 0) then (EMPTY 1)

EMPTY 0 FULL 0

Computer Organization Prof. H. Yoon

Central Processing Unit 11 Stack Organization

MEMORY STACK ORGANIZATION

1000

Memory with Program, Data, Program

PC (instructions)

and Stack Segments

Data

AR (operands)

3000

stack

3997

- A portion of memory is used as a stack with a 3998

3999

processor register as a stack pointer 4000

4001

SP

Stack grows

- PUSH: SP SP - 1 In this direction

M[SP] DR

- POP: DR M[SP]

SP SP + 1

Computer Organization Prof. H. Yoon

Central Processing Unit 12

REVERSE POLISH NOTATION

• Stack organization is very effective for evaluating

arithmetic expressions.

• The common arithmetic expression are written in

infinix notation, with each operator written between

the operands

Computer Organization Prof. H. Yoon

Central Processing Unit 13 Stack Organization

REVERSE POLISH NOTATION

• Arithmetic Expressions: A + B

A+B Infix notation

+AB Prefix or Polish notation

AB+ Postfix or reverse Polish notation

- The reverse Polish notation is very suitable for stack

manipulation

• Evaluation of Arithmetic Expressions

Any arithmetic expression can be expressed in parenthesis-free

Polish notation, including reverse Polish notation

(3 * 4) + (5 * 6) 34*56*+

6

4 5 5 30

3 3 12 12 12 12 42

3 4 * 5 6 * +

Computer Organization Prof. H. Yoon

Central Processing Unit 14

PROCESSOR ORGANIZATION

• In general, most processors are organized in one of 3 ways

– Single register (Accumulator) organization

» Basic Computer is a good example

» Accumulator is the only general purpose register

– General register organization

» Used by most modern computer processors

» Any of the registers can be used as the source or destination for

computer operations

– Stack organization

» All operations are done using the stack

» For example, an OR instruction will pop the two top elements from the

stack, do a logical OR on them, and push the result on the stack

Computer Organization Prof. H. Yoon

Central Processing Unit 15 Addressing Modes

ADDRESSING MODES

• Addressing Modes

* Specifies a rule for interpreting or modifying the

address field of the instruction (before the operand

is actually referenced)

* Variety of addressing modes

- to give programming flexibility to the user

- to use the bits in the address field of the

instruction efficiently

Computer Organization Prof. H. Yoon

Central Processing Unit 16

Computer Organization Prof. H. Yoon

Central Processing Unit 17 Addressing Modes

TYPES OF ADDRESSING MODES

• Implied Mode

- Address of the operands are specified implicitly in the instruction

- No need to specify address in the instruction

- Data is the part of instruction

Example: Complement AC

• Immediate Mode

Instead of specifying the address of the operand, operand itself is specified

- No need to specify address in the instruction

- However, operand itself needs to be specified

- Fast to acquire an operand

Computer Organization Prof. H. Yoon

Central Processing Unit 18 Addressing Modes

TYPES OF ADDRESSING MODES

• Register Mode

Address specified in the instruction is the register address

- Designated operand need to be in a register

- Shorter address than the memory address

- Saving address field in the instruction

- Faster to acquire an operand than the memory addressing

- EA = IR(R) (IR(R): Register field of IR)

• Register Indirect Mode

Instruction specifies a register which contains the memory address of

the operand

- Saving instruction bits since register address is shorter than the memory

address

- Slower to acquire an operand than both the register addressing or memory

addressing

- EA = [IR(R)] ([x]: Content of x)

• Autoincrement or Autodecrement Mode

- When the address in the register is used to access memory, the value in

the register is incremented or decremented by 1 automatically

Computer Organization Prof. H. Yoon

Central Processing Unit 19 Addressing Modes

TYPES OF ADDRESSING MODES

• Direct Address Mode

Instruction specifies the memory address which can be used directly to

access the memory

- Faster than the other memory addressing modes

- Too many bits are needed to specify the address for a large physical

memory space

- EA = IR(addr) (IR(addr): address field of IR)

• Indirect Addressing Mode

The address field of an instruction specifies the address of a memory

location that contains the address of the operand

- Slow to acquire an operand because of an additional memory access

- EA = M[IR(address)]

Computer Organization Prof. H. Yoon

Central Processing Unit 20 Addressing Modes

TYPES OF ADDRESSING MODES

• Relative Addressing Modes

The Address fields of an instruction specifies the part of the address

to calculate the address of the operand

- Address field of the instruction is short

- Large physical memory can be accessed with a small number of

address bits

- EA = IR (address + PC)

3 different Relative Addressing Modes depending on R;

* PC Relative Addressing Mode (R = PC)

- EA = PC + IR(address)

* Indexed Addressing Mode (R = IX, where IX: Index Register)

- EA = IX + IR(address)

* Base Register Addressing Mode

(R = BAR, where BAR: Base Address Register)

- EA = BAR + IR(address)

Computer Organization Prof. H. Yoon

Central Processing Unit 21

Numerical

• The two-word instruction at address 200 and 201 is a

“load to AC” instruction with an address field equal to

500. The first word of the instruction specifies the

operation code and mode, and the second word specifies

the address part. PC has the value 200 for fetching this

instruction. The content of processor register R1 is 400,

and the content of an index register XR is 100. AC

receives the operand after the instruction is executed.

• Calculate the operand values for all modes.

Computer Organization Prof. H. Yoon

Central Processing Unit 22

Computer Organization Prof. H. Yoon

Central Processing Unit 23

Computer Organization Prof. H. Yoon

Central Processing Unit 24 Addressing Modes

ADDRESSING MODES - EXAMPLES -

Address Memory

300 Load to AC Mode

PC = 200 301 Address = 400

MODE LOAD TO AC 399 202 Next instruction

R1 = 200

399 450

XR = 100

400 700

AC

500 800

600 900

Addressing Effective Content 700 325

Mode Address of AC

Direct address 500 /* AC (500) */ 800

Immediate operand - /* AC 500 */ 500 800 300

Indirect address 800 /* AC ((500)) */ 300

Relative address 702 /* AC (PC+500) */ 325

Indexed address 600 /* AC (XR+500) */ 900

Register - /* AC R1 */ 400

Register indirect 400 /* AC (R1) */ 700

Autoincrement 400 /* AC (R1)+ */ 700

Autodecrement 399 /* AC -(R1) */ 450

Computer Organization Prof. H. Yoon

Central Processing Unit 25

DATA TRANSFER INSTRUCTIONS

• Computers provide an extensive set of instructions to

give the user flexibility to carry out various computational

tasks.

• Most computer instructions can be classifies into three

categories.

1. Data transfer instructions

2. Data manipulation instruction

3. Program control instruction

Computer Organization Prof. H. Yoon

Central Processing Unit 26 Data Transfer and Manipulation

DATA MANIPULATION INSTRUCTIONS

Data manipulation instruction

• Arithmetic Instructions

Name Mnemonic

Increment INC

Decrement DEC

Add ADD

Subtract SUB

Multiply MUL

Divide DIV

Add with Carry ADDC

Subtract with Borrow SUBB

Negate(2’s Complement) NEG

• Logical and Bit Manipulation Instructions • Shift Instructions

Name Mnemonic Name Mnemonic

Clear CLR Logical shift right SHR

Complement COM Logical shift left SHL

AND AND Arithmetic shift right SHRA

OR OR Arithmetic shift left SHLA

Exclusive-OR XOR Rotate right ROR

Clear carry CLRC Rotate left ROL

Set carry SETC Rotate right thru carry RORC

Complement carry COMC Rotate left thru carry ROLC

Enable interrupt EI

Disable interrupt DI

Computer Organization Prof. H. Yoon

Central Processing Unit 27

Computer Organization Prof. H. Yoon

Central Processing Unit 28 RISC

RISC: Historical Background

IBM System/360, 1964

• The real beginning of modern computer architecture

• Distinction between Architecture and Implementation

• Architecture: The abstract structure of a computer

seen by an assembly-language programmer

Hardware

-program

Compiler

High-Level Instruction

Language Hardware

Set

Architecture

Hardware

Implementation

• Continuing growth in semiconductor memory and

microprogramming

A much richer and complicated instruction sets

CISC (Complex Instruction Set Computer)

Computer Organization Prof. H. Yoon

Central Processing Unit 29

RISC

• RISC (reduced instruction set computer) is a number of

types of computer instructions so that it can operate at a

higher speed (perform more millions of instructions per

second, or MIPS).

• A larger list or set of computer instructions tends to make

the microprocessor more complicated and slower in

operation.

• RISC chips require fewer transistors which make them

cheaper to design and produce.

Computer Organization Prof. H. Yoon

Central Processing Unit 30

Complex Instruction Set Computing

• A complex instruction set computer is a computer where

single instructions can perform numerous low-level

operations like a load from memory, an arithmetic

operation, and a memory store or are accomplished by

multi-step processes or addressing modes in single

instructions, as its name proposes “Complex Instruction

Set ”.

• It has a huge number of compound instructions, which

takes a long time to perform.

• Here, a single set of instruction is protected in several

steps; each instruction set has additional than 300

separate instructions. Maximum instructions are finished

in two to ten machine cycles. In CISC, instruction

pipelining is not easily implemented.

Computer Organization Prof. H. Yoon

Central Processing Unit 31

Difference Between RISC & CISC

Computer Organization Prof. H. Yoon

Central Processing Unit 32

Computer Organization Prof. H. Yoon

Central Processing Unit 33 RISC

ARCHITECTURE DESIGN PRINCIPLES - IN 70’s -

• Large microprograms would add little or nothing

to the cost of the machine

Rapid growth of memory technology

Large General Purpose Instruction Set

• Microprogram is much faster than the machine instructions

Microprogram memory is much faster than main memory

Moving the software functions into

microprogram for the high performance machines

• Execution speed is proportional to the program size

Architectural techniques that led to small program

High performance instruction set

• Number of registers in CPU has limitations

Very costly

Difficult to utilize them efficiently

Computer Organization Prof. H. Yoon

Central Processing Unit 34 RISC

FOUR MODERN ARCHITECTURES IN 70’s

DEC Xerox Intel

IBM 370/168 VAX-11/780 Dorado iAPX-432

Year 1973 1978 1978 1982

# of instrs. 208 303 270 222

Control mem. size 420 Kb 480 Kb 136 Kb 420 Kb

Instr. size (bits) 16-48 16-456 8-24 6-321

Technology ECL MSI TTL MSI ECL MSI NMOS VLSI

Execution model reg-mem reg-mem stack stack

mem-mem mem-mem mem-mem

reg-reg reg-reg

Cache size 64 Kb 64 Kb 64 Kb 64 Kb

Computer Organization Prof. H. Yoon

Central Processing Unit 35

VARIABLE LENGTH INSTRUCTIONS

• The large number of instructions and addressing

modes led CISC machines to have variable length

instruction formats

• The large number of instructions means a greater

number of bits to specify them

• In order to manage this large number of opcodes

efficiently, they were encoded with different lengths:

– More frequently used instructions were encoded using short opcodes.

– Less frequently used ones were assigned longer opcodes.

Computer Organization Prof. H. Yoon

Central Processing Unit 36

REDUCED INSTRUCTION SET COMPUTERS

• In the late ‘70s and early ‘80s there was a reaction to the

shortcomings of the CISC style of processors

• Reduced Instruction Set Computers (RISC) were proposed as

an alternative

• The underlying idea behind RISC processors is to simplify the

instruction set and reduce instruction execution time

• RISC processors often feature:

– Few instructions

– Few addressing modes

– Only load and store instructions access memory

– All other operations are done using on-processor registers

– Fixed length instructions

– Single cycle execution of instructions

– The control unit is hardwired, not microprogrammed

Computer Organization Prof. H. Yoon

Central Processing Unit 37

PIPELINING

• A very important feature of many RISC processors is the ability to

execute an instruction each clock cycle

• This may seem nonsensical, since it takes at least once clock cycle

each to fetch, decode and execute an instruction.

• It is however possible, because of a technique known as pipelining

– We’ll study this in detail later

• Pipelining is the use of the processor to work on different phases of

multiple instructions in parallel

• So, if we’re running three instructions at once, and it takes an average

instruction three cycles to run, the CPU is executing an average of an

instruction a clock cycle

Computer Organization Prof. H. Yoon

Central Processing Unit 38

REGISTERS

• By having a large number of general purpose registers, a

processor can minimize the number of times it needs to access

memory to load or store a value

• This results in a significant speed up, since memory accesses

are much slower than register accesses

• Register accesses are fast, since they just use the bus on the

CPU itself, and any transfer can be done in one clock cycle

• To go off-processor to memory requires using the much slower

memory (or system) bus

• It may take many clock cycles to read or write to memory

across the memory bus

– The memory bus hardware is usually slower than the processor

– There may even be competition for access to the memory bus by other

devices in the computer (e.g. disk drives)

• So, for this reason alone, a RISC processor may have an

advantage over a comparable CISC processor, since it only

needs to access memory

– for its instructions, and

– occasionally to load or store a memory value

Computer Organization Prof. H. Yoon

You might also like

- Unit 2-2Document30 pagesUnit 2-2kiran281196No ratings yet

- Computer Organization and Design: Lecture: 3 Tutorial: 1 Practical: 0 Credit: 4Document25 pagesComputer Organization and Design: Lecture: 3 Tutorial: 1 Practical: 0 Credit: 4Æ Reddy VïñødNo ratings yet

- Ch8, Central Processing UnitDocument61 pagesCh8, Central Processing UnitKavita DagarNo ratings yet

- CH 8Document61 pagesCH 8Mustafa AdilNo ratings yet

- Ch8 - Central Processing UnitDocument61 pagesCh8 - Central Processing Unitganjoo.pregyaNo ratings yet

- CH - 0820 4 2017Document24 pagesCH - 0820 4 2017premNo ratings yet

- Module 4Document35 pagesModule 4ajajaNo ratings yet

- ch8 Cpu NewDocument48 pagesch8 Cpu New03Abhishek SharmaNo ratings yet

- General Register Organization Stack Organization Addressing Modes Data Transfer and Manipulation Program Control Risc and CiscDocument46 pagesGeneral Register Organization Stack Organization Addressing Modes Data Transfer and Manipulation Program Control Risc and Ciscyogesh kumarNo ratings yet

- Unit 3 CompleteDocument60 pagesUnit 3 CompleteAaditya Raj PandeyNo ratings yet

- A289676274 23825 16 2019 Chapter4Document33 pagesA289676274 23825 16 2019 Chapter4Satyam AnandNo ratings yet

- Coa Unit1 (Part2)Document43 pagesCoa Unit1 (Part2)shubham singhalNo ratings yet

- Unit 3Document38 pagesUnit 3manikanta.reddy329No ratings yet

- Central Processing UnitDocument10 pagesCentral Processing UnitManoj Reddy GudaNo ratings yet

- Central Processing UnitDocument33 pagesCentral Processing UnitSatyam AnandNo ratings yet

- Unit 4Document31 pagesUnit 4Vishal VatsavNo ratings yet

- Unit3 CPUDocument40 pagesUnit3 CPUKrishna VamsiNo ratings yet

- Central Processing Unit: - IntroductionDocument31 pagesCentral Processing Unit: - Introductionsara_loloNo ratings yet

- UNIT 3 Ca (EASY)Document75 pagesUNIT 3 Ca (EASY)Anugrah KumarNo ratings yet

- Register - Stack Organisation 2Document10 pagesRegister - Stack Organisation 2Syed Rasheed uddinNo ratings yet

- Chapter 8: Central Processing Unit: Cpe 252: Computer Organization 1Document30 pagesChapter 8: Central Processing Unit: Cpe 252: Computer Organization 1Tanvi SharmaNo ratings yet

- Unit 3 JSPSinghDocument55 pagesUnit 3 JSPSinghAryan RathoreNo ratings yet

- Chapter Two Assembly Programming NoteDocument30 pagesChapter Two Assembly Programming NoteMunir AliNo ratings yet

- COA Ch4 CpuDocument42 pagesCOA Ch4 Cpueba girmaNo ratings yet

- M5 Part 1Document30 pagesM5 Part 1HarsshithaNo ratings yet

- Central Processing UnitDocument22 pagesCentral Processing UnitdatalogdigitalNo ratings yet

- Chapter 8Document31 pagesChapter 8nidz2245No ratings yet

- Cao Notes Mca First SemDocument31 pagesCao Notes Mca First SemANKUR CHOUDHARYNo ratings yet

- Register OrgaDocument15 pagesRegister OrgaKannan KannanNo ratings yet

- Computer Architecture Unit 1Document35 pagesComputer Architecture Unit 1agamer43387No ratings yet

- Chapter 8Document30 pagesChapter 8Saifullah BhuttoNo ratings yet

- CH-1.Central Processing UnitDocument75 pagesCH-1.Central Processing UnitDevanshi GudsariyaNo ratings yet

- Unit 3 Notes CADocument32 pagesUnit 3 Notes CAAnugrah KumarNo ratings yet

- Notes Computer System Organization Unit 1Document11 pagesNotes Computer System Organization Unit 1Grace PatelNo ratings yet

- Computer Architecture & Organization: 8/5/2010 Ajay Kumar Singh@FET 1Document9 pagesComputer Architecture & Organization: 8/5/2010 Ajay Kumar Singh@FET 1Ajay Kumar SinghNo ratings yet

- CH 3 MaterialDocument30 pagesCH 3 MaterialS20CP61 Ayushi GoswamiNo ratings yet

- Chapter 3 Lecture 1 Central Processing UnitDocument37 pagesChapter 3 Lecture 1 Central Processing UnitIsiyak SolomonNo ratings yet

- Lecture 12 - General Register OrganizationDocument6 pagesLecture 12 - General Register OrganizationPragya SinghNo ratings yet

- General Register OrganizationDocument9 pagesGeneral Register OrganizationDivyaanshu AgrawalNo ratings yet

- COA GTU Study Material Presentations Unit-5 11022020053257AMDocument64 pagesCOA GTU Study Material Presentations Unit-5 11022020053257AMJanvi PatelNo ratings yet

- Central Processing UnitDocument7 pagesCentral Processing UnitMohit SinghNo ratings yet

- Module IV LOCDocument21 pagesModule IV LOCrahulNo ratings yet

- Central Processing UnitDocument49 pagesCentral Processing UnitFaizal KhanNo ratings yet

- Coa 4th LessonDocument23 pagesCoa 4th LessonMukeshNo ratings yet

- A Brief Introduction of Microcontrollers: 8051 MicrocontrollerDocument67 pagesA Brief Introduction of Microcontrollers: 8051 Microcontrollerapi-19786583No ratings yet

- D KannanDocument35 pagesD Kannanpreneeth Ramesh007No ratings yet

- General Purpose RegisterDocument7 pagesGeneral Purpose Registersaumya2213215No ratings yet

- Seven Cpu RegistersDocument6 pagesSeven Cpu RegistersPriyanka PuvvalaNo ratings yet

- MODULE 6iiaDocument27 pagesMODULE 6iiaShelton MhondiwaNo ratings yet

- File 1693830933 GUSCSE202332280 L6-ComputerOrganizationandArchitectureDocument8 pagesFile 1693830933 GUSCSE202332280 L6-ComputerOrganizationandArchitecturegauravyadav24022004No ratings yet

- Coa Unit 5Document73 pagesCoa Unit 5Shiv Patel 18-38No ratings yet

- 8051 Microcontroller Instruction Set: Electronics HubDocument12 pages8051 Microcontroller Instruction Set: Electronics Hubibrar saqibNo ratings yet

- Chapter5 2Document37 pagesChapter5 2preneeth Ramesh007No ratings yet

- Datapath3 1upDocument26 pagesDatapath3 1upJaydeep RajputNo ratings yet

- Lecture 8Document26 pagesLecture 8Pranav ChauhanNo ratings yet

- Chapter 4 PLC Programming PDFDocument100 pagesChapter 4 PLC Programming PDFmiraNo ratings yet

- Relational Database Index Design and the Optimizers: DB2, Oracle, SQL Server, et al.From EverandRelational Database Index Design and the Optimizers: DB2, Oracle, SQL Server, et al.Rating: 5 out of 5 stars5/5 (1)

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationFrom EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNo ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- C96-98-3640 Error Codes (917 Error Fatal) PDFDocument4 pagesC96-98-3640 Error Codes (917 Error Fatal) PDFArmandoPerezNo ratings yet

- Week 4 HomeworkDocument2 pagesWeek 4 HomeworkJohn Monnahan100% (1)

- Memory Selection of ESDocument37 pagesMemory Selection of ESAravind YadavNo ratings yet

- Beep Error CodesDocument2 pagesBeep Error CodesRhoda SanchezNo ratings yet

- Mca R16-Scet SyllabusDocument135 pagesMca R16-Scet SyllabusSiva KiranNo ratings yet

- Automation Using PLCDocument32 pagesAutomation Using PLCRamashish KumarNo ratings yet

- Ensoniq ESQ-m To SQ80m Wiring Diagram / Install GuideDocument1 pageEnsoniq ESQ-m To SQ80m Wiring Diagram / Install GuidepowerbrokerNo ratings yet

- Dev ListDocument12 pagesDev Listtrixum_890No ratings yet

- Rfid Access Control System and Security WebcamDocument6 pagesRfid Access Control System and Security WebcamAjay BhaleraoNo ratings yet

- FALLSEM2022-23 BECE102L TH VL2022230102871 Reference Material I 05-10-2022 22. Analysis of Clocked Sequential CircuitsDocument17 pagesFALLSEM2022-23 BECE102L TH VL2022230102871 Reference Material I 05-10-2022 22. Analysis of Clocked Sequential CircuitsAakashNo ratings yet

- Implementing A Multi-Domain System: Siemens Digital Industries SoftwareDocument9 pagesImplementing A Multi-Domain System: Siemens Digital Industries SoftwareOscar MendozaNo ratings yet

- Chapter 6 - Expansion BusDocument6 pagesChapter 6 - Expansion Busapi-3750451100% (1)

- 945P-A/ 945PL-A: Page Title of SchematicDocument40 pages945P-A/ 945PL-A: Page Title of SchematicАндрей АндреевNo ratings yet

- Lecture Notes On Parallel Processing PipelineDocument12 pagesLecture Notes On Parallel Processing PipelineYowaraj ChhetriNo ratings yet

- A Project Synopsis: Mobile Password Activation System For Industrial ApplicationsDocument18 pagesA Project Synopsis: Mobile Password Activation System For Industrial Applicationslokesh_045No ratings yet

- Cutsheet xp8Document2 pagesCutsheet xp8Carlos BonattoNo ratings yet

- Computer Architecture MCQ SDocument19 pagesComputer Architecture MCQ SAbdulRehmanNo ratings yet

- DevlistDocument6 pagesDevlistVineeth NallachervuNo ratings yet

- 01 Introduction Embedded System DesignDocument32 pages01 Introduction Embedded System DesignPAUL SATHIYANNo ratings yet

- Operating Instructions RS422/RS485 Interface (Part No. 5954201)Document2 pagesOperating Instructions RS422/RS485 Interface (Part No. 5954201)مراد احمدNo ratings yet

- Remote Controlled FanDocument4 pagesRemote Controlled FanJostin PunnasseryNo ratings yet

- S29CD016G: 16 Megabit (512 K X 32-Bit) CMOS 2.5 Volt-Only Burst Mode, Dual Boot, Simultaneous Read/Write Flash MemoryDocument91 pagesS29CD016G: 16 Megabit (512 K X 32-Bit) CMOS 2.5 Volt-Only Burst Mode, Dual Boot, Simultaneous Read/Write Flash Memoryyeison parraNo ratings yet

- Syllabus MicrocontrollerDocument3 pagesSyllabus MicrocontrollerharshithaNo ratings yet

- Quadrature To Rs232 CardDocument8 pagesQuadrature To Rs232 Cardtomjordan12321No ratings yet

- 8gb Gddr5 Sgram BriefDocument7 pages8gb Gddr5 Sgram BriefsamimikuNo ratings yet

- Chapter 2 COM101Document5 pagesChapter 2 COM101Christean Val Bayani ValezaNo ratings yet

- COE 538 Ryerson UniversityDocument6 pagesCOE 538 Ryerson Universityunited_n72No ratings yet

- Computer Architecture Elementary Pipelining StudyDocument20 pagesComputer Architecture Elementary Pipelining StudyJordan D. Ulmer100% (4)

- UARTDocument26 pagesUARTShantanu Tripathi100% (2)

- CL gd542xDocument104 pagesCL gd542xgoryachev5No ratings yet