Professional Documents

Culture Documents

Minimizing Leakage Power-I

Minimizing Leakage Power-I

Uploaded by

Abdul Munaf0 ratings0% found this document useful (0 votes)

4 views23 pagesThis document discusses approaches to minimize leakage power in integrated circuits. It covers why leakage power has become an issue with scaling, how threshold voltage scaling affects leakage, and techniques for fabricating multiple threshold voltages including multiple channel doping, oxide thickness, channel length, and body bias. It also summarizes approaches for leakage reduction including transistor stacking, VTCMOS, and MTCMOS. Simulation results are presented and advantages/limitations of MTCMOS are discussed. References for further reading on the topic are provided.

Original Description:

Copyright

© © All Rights Reserved

Available Formats

PPTX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThis document discusses approaches to minimize leakage power in integrated circuits. It covers why leakage power has become an issue with scaling, how threshold voltage scaling affects leakage, and techniques for fabricating multiple threshold voltages including multiple channel doping, oxide thickness, channel length, and body bias. It also summarizes approaches for leakage reduction including transistor stacking, VTCMOS, and MTCMOS. Simulation results are presented and advantages/limitations of MTCMOS are discussed. References for further reading on the topic are provided.

Copyright:

© All Rights Reserved

Available Formats

Download as PPTX, PDF, TXT or read online from Scribd

Download as pptx, pdf, or txt

0 ratings0% found this document useful (0 votes)

4 views23 pagesMinimizing Leakage Power-I

Minimizing Leakage Power-I

Uploaded by

Abdul MunafThis document discusses approaches to minimize leakage power in integrated circuits. It covers why leakage power has become an issue with scaling, how threshold voltage scaling affects leakage, and techniques for fabricating multiple threshold voltages including multiple channel doping, oxide thickness, channel length, and body bias. It also summarizes approaches for leakage reduction including transistor stacking, VTCMOS, and MTCMOS. Simulation results are presented and advantages/limitations of MTCMOS are discussed. References for further reading on the topic are provided.

Copyright:

© All Rights Reserved

Available Formats

Download as PPTX, PDF, TXT or read online from Scribd

Download as pptx, pdf, or txt

You are on page 1of 23

UNIT-V (LEAKAGE POWER

MINIMIZATION APPROACHES)

LECTURE-1

MINIMIZING

LEAKAGE POWER-I

Dept of ECE, IIIT-RK Valley, RGUKT

AGENDA

2

Dept of ECE, IIIT-RK Valley, RGUKT

Why Leakage Power is an Issue?

3

Dept of ECE, IIIT-RK Valley, RGUKT

Leakage Power Limits Vt Scaling

4

Dept of ECE, IIIT-RK Valley, RGUKT

Key Parameter Vt

5

Dept of ECE, IIIT-RK Valley, RGUKT

Threshold Voltage(Vt) Scaling

6

Dept of ECE, IIIT-RK Valley, RGUKT

Fabrication of Multiple Threshold Voltages:

7

Multiple Channel Doping

Multiple Oxide thickness

Multiple channel length

Multiple Body bias

Dept of ECE, IIIT-RK Valley, RGUKT

Multiple Channel Doping

8

Dept of ECE, IIIT-RK Valley, RGUKT

Multiple Oxide Thickness

9

Dept of ECE, IIIT-RK Valley, RGUKT

Multiple channel length

10

Dept of ECE, IIIT-RK Valley, RGUKT

Multiple Body bias

11

Dept of ECE, IIIT-RK Valley, RGUKT

Leakage Reduction Approaches

12

Dept of ECE, IIIT-RK Valley, RGUKT

Transistor Stacking

13

Dept of ECE, IIIT-RK Valley, RGUKT

Transistor Stacking : 3 I/P Nand Gate

14

Dept of ECE, IIIT-RK Valley, RGUKT

Transistor Stacking

15

Dept of ECE, IIIT-RK Valley, RGUKT

Transistor Stacking

16

Dept of ECE, IIIT-RK Valley, RGUKT

VTCMOS:

17

Dept of ECE, IIIT-RK Valley, RGUKT

VTCMOS Approach:

18

Dept of ECE, IIIT-RK Valley, RGUKT

MTCMOS

19

Dept of ECE, IIIT-RK Valley, RGUKT

MTCMOS

20

Dept of ECE, IIIT-RK Valley, RGUKT

Simulation Results

21

Dept of ECE, IIIT-RK Valley, RGUKT

Advantages & Limitations of MTCMOS

22

Dept of ECE, IIIT-RK Valley, RGUKT

References

23

Title : Low-Power VLSI Circuits & Systems

Author : Ajit Pal

Edition : Illustrated

Publisher : Springer, 2014

ISBN : 8132219376, 9788132219378

Dept of ECE, IIIT-RK Valley, RGUKT

You might also like

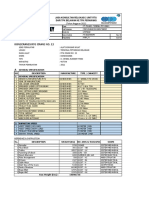

- Relay Setting Calculation Rev.1 PDFDocument113 pagesRelay Setting Calculation Rev.1 PDFtarik.taspinar87% (30)

- Moment Influence Line ReportDocument13 pagesMoment Influence Line Reporthaziq khairudin33% (3)

- Mfg. Of: LT Panel, APFC, AMF, PCC, MCC, Street Light Panel, High Mast Panel, Automation PanelDocument5 pagesMfg. Of: LT Panel, APFC, AMF, PCC, MCC, Street Light Panel, High Mast Panel, Automation PanelRajesh PatelNo ratings yet

- Notification of Safety Precautions: GeneraDocument17 pagesNotification of Safety Precautions: GeneraBalakrishnan Krishnan0% (1)

- Minimizing Leakage Power-IDocument25 pagesMinimizing Leakage Power-IPULAGAMPALLI MANJULANo ratings yet

- CAD Tools For Low PowerDocument29 pagesCAD Tools For Low PowerSEHARABANU MULLANo ratings yet

- Variation Tolerant DesignDocument30 pagesVariation Tolerant DesignAbdul MunafNo ratings yet

- Unit-Vi (Special Topics) : Lecture-2 Adiabatic Logic CircuitsDocument24 pagesUnit-Vi (Special Topics) : Lecture-2 Adiabatic Logic CircuitsSEHARABANU MULLANo ratings yet

- Adiabatic Logic CircuitsDocument25 pagesAdiabatic Logic CircuitsAbdul MunafNo ratings yet

- Nu3-Ktrg: 1e/TG 4E/ "Document1 pageNu3-Ktrg: 1e/TG 4E/ "Raju ReddyNo ratings yet

- Less Than Three Vendors of RdsoDocument11 pagesLess Than Three Vendors of RdsoYOU COMFY YOU LOSENo ratings yet

- Lampiran 2. Survey Kondisi Dan Local Part IdentificationDocument8 pagesLampiran 2. Survey Kondisi Dan Local Part IdentificationKONSULTAN RELOKASI RTGNo ratings yet

- 1 Proposed Utilities Building (Pcwbs-A610) : Short-Circuit AnalysisDocument17 pages1 Proposed Utilities Building (Pcwbs-A610) : Short-Circuit AnalysismuthukumarNo ratings yet

- 1557290920125-New Technologies Used in DFC Project by Ashutosh RankawatDocument26 pages1557290920125-New Technologies Used in DFC Project by Ashutosh RankawatMd. Shiraz JinnathNo ratings yet

- RECODocument32 pagesRECOAnonymous H67muZENo ratings yet

- EMIDocument27 pagesEMIBabuji Babuji RNo ratings yet

- Energex Estimation GuideDocument88 pagesEnergex Estimation GuideCarl James GranadaNo ratings yet

- Axle Counter Modern ChallengesDocument23 pagesAxle Counter Modern ChallengesRandy DityoNo ratings yet

- (Sankara Subramanian) GE Presentation - august2021-SENTDocument37 pages(Sankara Subramanian) GE Presentation - august2021-SENTzahra farrasNo ratings yet

- Supervised Industrial Training Report: National Transmission and Despatch Company (NTDC) PakistanDocument56 pagesSupervised Industrial Training Report: National Transmission and Despatch Company (NTDC) PakistanMarina KhanNo ratings yet

- 500kv 220kv, NTDC, Grid Station Gatti Faisalabad.Document56 pages500kv 220kv, NTDC, Grid Station Gatti Faisalabad.Cheap but good100% (3)

- 500kv Rawat Pakistan Audit ReportDocument9 pages500kv Rawat Pakistan Audit ReportAsad KhanNo ratings yet

- 1616585316635-TKD Shed RTIDocument29 pages1616585316635-TKD Shed RTIMD NADEEMNo ratings yet

- E05 OHL-1 CT (Modified)Document3 pagesE05 OHL-1 CT (Modified)arunNo ratings yet

- Kz4e KPTCL Srinivasapura Mod 15-02-24draft MomDocument9 pagesKz4e KPTCL Srinivasapura Mod 15-02-24draft MomREDDY SANDEEPNo ratings yet

- PTN 6300 Packet Transport Product Hardware IntroductionDocument39 pagesPTN 6300 Packet Transport Product Hardware IntroductionLovaNo ratings yet

- Ilstrwy15: CAMPINAS / Viracopos, INTL (SBKP) Carta de Aproxima O Por Instrumentos (Iac)Document1 pageIlstrwy15: CAMPINAS / Viracopos, INTL (SBKP) Carta de Aproxima O Por Instrumentos (Iac)Guilherme Kazuo OgawaNo ratings yet

- PLCC System PresentationDocument31 pagesPLCC System Presentationgauravagarwal0141No ratings yet

- WEST - QURNA-2 - GTPP - PHASE - 2 - LC-3 - LC-4 - Prot Coord Report - 20230922 - 024801Document13 pagesWEST - QURNA-2 - GTPP - PHASE - 2 - LC-3 - LC-4 - Prot Coord Report - 20230922 - 024801kohgilozadehkazemNo ratings yet

- Capex Cal 120 ParkingDocument7 pagesCapex Cal 120 ParkingDarshit VyasNo ratings yet

- Proclim ATOM VRF Multi 2020 - CompressedDocument114 pagesProclim ATOM VRF Multi 2020 - CompressedBabi Dou100% (1)

- Petrobras P-55 SCR DesingDocument6 pagesPetrobras P-55 SCR DesingJuan LopezNo ratings yet

- Application of PLCDocument37 pagesApplication of PLCSupriya YenniNo ratings yet

- Study of Top Quark Pair and Calculating The Top Mass: Joydeep NaskarDocument13 pagesStudy of Top Quark Pair and Calculating The Top Mass: Joydeep NaskarJoydeep NaskarNo ratings yet

- Prentation by CMT On Liquid Handling JNPADocument16 pagesPrentation by CMT On Liquid Handling JNPAMelvin EldhoseNo ratings yet

- Thales Axle Counter: The Challenges For A Modern Train Detection SystemDocument23 pagesThales Axle Counter: The Challenges For A Modern Train Detection SystemKhuyến TrầnNo ratings yet

- 5th Protection AgendaDocument9 pages5th Protection Agendagholapnc1040No ratings yet

- Final IndexDocument30 pagesFinal Indexaravindhana1a1No ratings yet

- Method Statement For Temporary Access Road (Towayya) - (Rev.)Document14 pagesMethod Statement For Temporary Access Road (Towayya) - (Rev.)skystar100% (1)

- 6.STC TRS Conventional 02 GH ContactorsDocument27 pages6.STC TRS Conventional 02 GH Contactorsmikkumar5No ratings yet

- Dynamic Pile Load Testing Experiences in PDFDocument14 pagesDynamic Pile Load Testing Experiences in PDFPurdiansyahNo ratings yet

- Guard Pond: 08-Dec-14 JBF Petrochemicals LTD 1Document5 pagesGuard Pond: 08-Dec-14 JBF Petrochemicals LTD 1SajeshKumarNo ratings yet

- Machines 03 00002Document25 pagesMachines 03 00002DrYs Kishore BabuNo ratings yet

- Gas Turbine Combustion and Power Generation: H.O.D, Mechanical Engg. S.R.I.M.TDocument79 pagesGas Turbine Combustion and Power Generation: H.O.D, Mechanical Engg. S.R.I.M.TYiro Renteria monjaNo ratings yet

- Quality AuditDocument1 pageQuality AuditDS ChaudharyNo ratings yet

- Bandreah CT-VT Sizing Calculation-Rev.ADocument110 pagesBandreah CT-VT Sizing Calculation-Rev.AJay WinNo ratings yet

- Sop For ProtoDocument7 pagesSop For ProtoDaniel GnanaselvamNo ratings yet

- IO List MRHSDocument52 pagesIO List MRHSvinayjoshi2705No ratings yet

- Wartsila SP A Id12 1 LLCDocument7 pagesWartsila SP A Id12 1 LLCJum Aswiny NatNo ratings yet

- Industrial Summar Training Report Mechanical Workshop. N.E. Railway GorkhpurDocument46 pagesIndustrial Summar Training Report Mechanical Workshop. N.E. Railway GorkhpurPawan KumarNo ratings yet

- Draft Common SSR 2019-20 .01-11-2019 APDocument186 pagesDraft Common SSR 2019-20 .01-11-2019 APvteja214No ratings yet

- Evaluating Dielectric Conditionin SF6 Gas BreakersDocument18 pagesEvaluating Dielectric Conditionin SF6 Gas BreakersGabriel Zenarosa Lacsamana100% (1)

- NTPC DPTDocument495 pagesNTPC DPTKuppan Srinivasan100% (1)

- Doc-Gis Floor - r1Document175 pagesDoc-Gis Floor - r1Anhera EnterpriseNo ratings yet

- BSPTCL SOR For 2018-19 Dt. 08.10.2018-FinalDocument41 pagesBSPTCL SOR For 2018-19 Dt. 08.10.2018-FinalChief Engineer TransOMNo ratings yet

- Electrical PresentationDocument29 pagesElectrical PresentationsatyanarayanaNo ratings yet

- Makelsan Trouble Shooting of Soft Start-Fault 15 - For SE 2-3kVADocument3 pagesMakelsan Trouble Shooting of Soft Start-Fault 15 - For SE 2-3kVAsahbi22100% (1)

- 115 Kv-34.5 KV Gis Substation MacanangDocument101 pages115 Kv-34.5 KV Gis Substation MacanangMark Ivan JagodillaNo ratings yet

- Gallium Nitride-enabled High Frequency and High Efficiency Power ConversionFrom EverandGallium Nitride-enabled High Frequency and High Efficiency Power ConversionGaudenzio MeneghessoNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Organizational Structures and The Performance of Supply Chain ManagementDocument23 pagesOrganizational Structures and The Performance of Supply Chain ManagementSerp YelmazNo ratings yet

- Lecture 1Document28 pagesLecture 1Topendra Bandhan100% (1)

- Sensores PDFDocument202 pagesSensores PDFJorge HerreraNo ratings yet

- SALBABIDADocument5 pagesSALBABIDACrisha Faith CanalijaNo ratings yet

- Black and White Minimalist Simple Design Freelancer ResumeDocument3 pagesBlack and White Minimalist Simple Design Freelancer Resumemalaz husseinNo ratings yet

- 3de e (Bocr) ManualDocument6 pages3de e (Bocr) ManualNaveen Gupta100% (1)

- Final Viva (Iec)Document13 pagesFinal Viva (Iec)Shaian IslamNo ratings yet

- Sony Ericsson PresentationDocument18 pagesSony Ericsson PresentationNayan158No ratings yet

- Business Model Innovation in A Circular Economy Reasons For Non-Acceptance of Circular Business ModelsDocument12 pagesBusiness Model Innovation in A Circular Economy Reasons For Non-Acceptance of Circular Business ModelsAndres ValdezNo ratings yet

- On The Ten-Year Success in The Application of Partial Extraction Therapy: A Systematic ReviewDocument9 pagesOn The Ten-Year Success in The Application of Partial Extraction Therapy: A Systematic ReviewDr Sharique AliNo ratings yet

- Sonalika ProjectDocument86 pagesSonalika ProjectVivek ThakurNo ratings yet

- Cost and Management Accounting Individual AssignmentDocument3 pagesCost and Management Accounting Individual AssignmentKIASHA NAIDUNo ratings yet

- Energy Savings Through Retrofit From Constant-Volume Terminal Reheat To Variable Air Volume SystemDocument5 pagesEnergy Savings Through Retrofit From Constant-Volume Terminal Reheat To Variable Air Volume Systemmashark2610No ratings yet

- Ome 664: Project Procurement and Contracting: LECTURE 1: Introduction To Procurement ManagementDocument46 pagesOme 664: Project Procurement and Contracting: LECTURE 1: Introduction To Procurement ManagementYonas AlemayehuNo ratings yet

- 2017 1 27 Governance Officer Temporary Agent AD 7antonis - fysekidisATgmail.com CV PDFDocument8 pages2017 1 27 Governance Officer Temporary Agent AD 7antonis - fysekidisATgmail.com CV PDFvvlakNo ratings yet

- Module Programming and Reprogramming Service Tips September 2013 Update V4Document1 pageModule Programming and Reprogramming Service Tips September 2013 Update V4Mauri accattoliNo ratings yet

- FILTROS Baldwin Product GuideDocument860 pagesFILTROS Baldwin Product GuideRodolfo LeonNo ratings yet

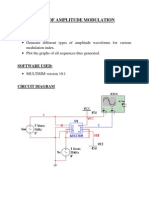

- Amplitude ModulationDocument14 pagesAmplitude ModulationMuralidhar NakkaNo ratings yet

- Networks of Touch A Tactile History of Chinese Art 1790 1840 Perspectives On Sensory History 1St Edition Hatch Full ChapterDocument67 pagesNetworks of Touch A Tactile History of Chinese Art 1790 1840 Perspectives On Sensory History 1St Edition Hatch Full Chapterheather.bekis553100% (12)

- Upgrading The Academic Performance Using Social Media of Grade 11 Ict Students in Kasiglahan Village Senior HighschoolDocument9 pagesUpgrading The Academic Performance Using Social Media of Grade 11 Ict Students in Kasiglahan Village Senior HighschoolSean NolonNo ratings yet

- (Integrated Circuits and Systems) Masashi Horiguchi, Kiyoo Itoh (Auth.) - Nanoscale Memory Repair-Springer-Verlag New York (2011)Document226 pages(Integrated Circuits and Systems) Masashi Horiguchi, Kiyoo Itoh (Auth.) - Nanoscale Memory Repair-Springer-Verlag New York (2011)SnehaNo ratings yet

- Valvula Alarma de 4 PulgadasDocument22 pagesValvula Alarma de 4 PulgadasRobertoNo ratings yet

- Tutorial 8Document14 pagesTutorial 8EdonNo ratings yet

- Deaerators: TEGO® AirexDocument8 pagesDeaerators: TEGO® AirexjoeNo ratings yet

- Cnchiwatec CatalogDocument16 pagesCnchiwatec Catalogriski utomoNo ratings yet

- CableDocument7 pagesCablerocketvtNo ratings yet

- Gases: Behavior & PropertiesDocument35 pagesGases: Behavior & PropertiesAdelia SetianingsihNo ratings yet

- PDF The History of Civil Engineering Philippines DDDocument47 pagesPDF The History of Civil Engineering Philippines DDRAIZZNo ratings yet

- End of Course PerameDocument2 pagesEnd of Course Perameramil damilesNo ratings yet