Professional Documents

Culture Documents

0 ratings0% found this document useful (0 votes)

4 viewsLecture 5a Pipelining

Lecture 5a Pipelining

Uploaded by

ryujindanceCopyright:

© All Rights Reserved

Available Formats

Download as PPT, PDF, TXT or read online from Scribd

You might also like

- Dell Color Laser Printer 2155CN Parts Service Manual PDFDocument1,048 pagesDell Color Laser Printer 2155CN Parts Service Manual PDFlmsserviceNo ratings yet

- Calix C7 R8.0 Provisioning GuideDocument586 pagesCalix C7 R8.0 Provisioning GuideKevin Upchurch100% (1)

- DDMDocument4 pagesDDMsengottaiyan100% (4)

- Assignment 1Document2 pagesAssignment 1Samira YomiNo ratings yet

- Pipelining Size and DepthDocument19 pagesPipelining Size and Depthwardabibi69No ratings yet

- Module 4Document12 pagesModule 4Bijay NagNo ratings yet

- Multipath 1 NotesDocument37 pagesMultipath 1 NotesNarender KumarNo ratings yet

- ILP - Appendix C PDFDocument52 pagesILP - Appendix C PDFDhananjay JahagirdarNo ratings yet

- CO2202 L14 CacheDocument31 pagesCO2202 L14 Cachevidsa2002No ratings yet

- 4-2 & 5-2 CompresorDocument20 pages4-2 & 5-2 CompresorJason MillerNo ratings yet

- Chapter 9 - Pipeline and Vector Processing Section 9.1 - Parallel ProcessingDocument10 pagesChapter 9 - Pipeline and Vector Processing Section 9.1 - Parallel Processingrajput12345No ratings yet

- Pipeline Processing CoaDocument34 pagesPipeline Processing Coahagos abateNo ratings yet

- Unit 4 - P 2Document13 pagesUnit 4 - P 2Sanju SanjayNo ratings yet

- Ovn MainDocument54 pagesOvn MainAvenir BajraktariNo ratings yet

- Operating Sytems: B.Tech Ii Yr (Term 08-09) Unit 2 PPT Slides Text BooksDocument52 pagesOperating Sytems: B.Tech Ii Yr (Term 08-09) Unit 2 PPT Slides Text BooksGopal KarmakarNo ratings yet

- Appendix ADocument93 pagesAppendix AzeewoxNo ratings yet

- Analytical Modeling of Parallel Systems: Ananth Grama, Anshul Gupta, George Karypis, and Vipin KumarDocument67 pagesAnalytical Modeling of Parallel Systems: Ananth Grama, Anshul Gupta, George Karypis, and Vipin KumarzoravarNo ratings yet

- Coa Module 3 Part 1Document42 pagesCoa Module 3 Part 1Ajith Bobby RajagiriNo ratings yet

- Exercise 4Document4 pagesExercise 4Mashavia AhmadNo ratings yet

- OOADDocument67 pagesOOADBobby JasujaNo ratings yet

- PipeliningDocument12 pagesPipeliningAradhyaNo ratings yet

- Project Review: by Vamsikrishna Chemudupati 14BEC0022Document35 pagesProject Review: by Vamsikrishna Chemudupati 14BEC0022VAMSIKRISHNA CHEMUDUPATI 14BEC0022No ratings yet

- Aca Module 2Document35 pagesAca Module 2Shiva prasad100% (1)

- Embedded Systems Design: Pipelining and Instruction SchedulingDocument48 pagesEmbedded Systems Design: Pipelining and Instruction SchedulingMisbah Sajid ChaudhryNo ratings yet

- 07 RTL Optimization TechniquesDocument20 pages07 RTL Optimization Techniquesgideontargrave7No ratings yet

- C F C P S (CS61063) : Tutorial 1Document13 pagesC F C P S (CS61063) : Tutorial 1brahma2deen2chaudharNo ratings yet

- Advance Electronics: UnacademyDocument38 pagesAdvance Electronics: UnacademyhemuNo ratings yet

- Pipelining: Advanced Computer ArchitectureDocument30 pagesPipelining: Advanced Computer ArchitectureShinisg Vava100% (1)

- Bash Course - Tutorial 4: Simulation Runtime ResultsDocument1 pageBash Course - Tutorial 4: Simulation Runtime Resultsanidcohen9058No ratings yet

- M116C 1 M116C 1 Lect02-PerformanceDocument23 pagesM116C 1 M116C 1 Lect02-PerformancetinhtrilacNo ratings yet

- Pipeline and Vector ProcessingDocument28 pagesPipeline and Vector ProcessingTerror BladeNo ratings yet

- Unit-V NEWDocument21 pagesUnit-V NEWsandhya vaniNo ratings yet

- Complexity Analysis Time-Space Trade-OffDocument51 pagesComplexity Analysis Time-Space Trade-OffJatin SinghNo ratings yet

- "Iron Law" of Processor Performance: Prof. R. Iris Bahar EN164 January 31, 2007Document4 pages"Iron Law" of Processor Performance: Prof. R. Iris Bahar EN164 January 31, 2007Charan Pratap SinghNo ratings yet

- Unit-4 Pipelinie and Vector ProcessingDocument33 pagesUnit-4 Pipelinie and Vector ProcessingMandeepNo ratings yet

- Parallel Computing Platforms: Chieh-Sen (Jason) HuangDocument21 pagesParallel Computing Platforms: Chieh-Sen (Jason) HuangBalakrishNo ratings yet

- Lecture: Pipelining BasicsDocument28 pagesLecture: Pipelining BasicsTahsin Arik TusanNo ratings yet

- Stud CSA Mod 5p2 Arithmetic SuperPipelineDocument57 pagesStud CSA Mod 5p2 Arithmetic SuperPipelinesheenaneesNo ratings yet

- Unit 5Document61 pagesUnit 5prototypes6341No ratings yet

- Pipelining: Basic and Intermediate ConceptsDocument69 pagesPipelining: Basic and Intermediate ConceptsmanibrarNo ratings yet

- Lecture 3: Performance/Power, MIPS InstructionsDocument18 pagesLecture 3: Performance/Power, MIPS Instructionskotewed571No ratings yet

- Pipeline ProcessingDocument28 pagesPipeline Processinganismitaray14No ratings yet

- 7th Sem Cim Module-III 3.2Document19 pages7th Sem Cim Module-III 3.2Abdul GaffarNo ratings yet

- 4 Instruction Set ArchitecturesDocument20 pages4 Instruction Set Architectures'Joenabie Maxey GamaoNo ratings yet

- DSP Architecture - Part 1Document36 pagesDSP Architecture - Part 1Sarabjeet SinghNo ratings yet

- CSO Computer ProgrammingDocument73 pagesCSO Computer ProgrammingAjNo ratings yet

- Exercise 3 & 12Document17 pagesExercise 3 & 12perreiragabriel172No ratings yet

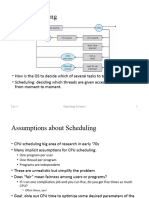

- 3 Process SchedulingDocument18 pages3 Process Schedulingmoin latifNo ratings yet

- Transport Control Protocol: OutlineDocument18 pagesTransport Control Protocol: OutlineSaranya BaskaranNo ratings yet

- CS-20002 (Os) - CS End April 2024Document13 pagesCS-20002 (Os) - CS End April 2024Shradha SwarupNo ratings yet

- Uni1-2 PipeliningDocument12 pagesUni1-2 PipeliningAditi VermaNo ratings yet

- Parallel Programming: in C With Mpi and Openmp Michael J. QuinnDocument73 pagesParallel Programming: in C With Mpi and Openmp Michael J. QuinnRohan PatilNo ratings yet

- 3 Process SchedulingDocument48 pages3 Process SchedulingAmit KumarNo ratings yet

- Lecture 3: Performance/Power, MIPS InstructionsDocument22 pagesLecture 3: Performance/Power, MIPS InstructionsHariharan SNo ratings yet

- A Scalable Approximate DCT Architecture For Efficient Hevc Compliant Video CodingDocument13 pagesA Scalable Approximate DCT Architecture For Efficient Hevc Compliant Video CodingvickyNo ratings yet

- Embedded Lecture 4 ARMDocument47 pagesEmbedded Lecture 4 ARMmsmukeshsinghmsNo ratings yet

- Hardware Realisation of A Computer System: Architecting SpeedDocument18 pagesHardware Realisation of A Computer System: Architecting SpeedMandy LoresNo ratings yet

- Mod6 2 PDFDocument15 pagesMod6 2 PDFsourav giriNo ratings yet

- HSE-3 Soc Chip Basics - ClearDocument50 pagesHSE-3 Soc Chip Basics - ClearUdayaJasperNo ratings yet

- Unit-5 (Coa) NotesDocument33 pagesUnit-5 (Coa) NotesyashNo ratings yet

- Numerical Methods for Simulation and Optimization of Piecewise Deterministic Markov Processes: Application to ReliabilityFrom EverandNumerical Methods for Simulation and Optimization of Piecewise Deterministic Markov Processes: Application to ReliabilityNo ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- Additional Problems 8Document2 pagesAdditional Problems 8ryujindanceNo ratings yet

- Additional Problems 6Document2 pagesAdditional Problems 6ryujindanceNo ratings yet

- Lecture 3b Verilog FSM ExamplesDocument19 pagesLecture 3b Verilog FSM ExamplesryujindanceNo ratings yet

- Module U3 - Risk Management V2Document12 pagesModule U3 - Risk Management V2ryujindanceNo ratings yet

- SEGMENT16 Switch StatementsDocument17 pagesSEGMENT16 Switch StatementsryujindanceNo ratings yet

- SEGMENT15 Predicated IndirectDocument5 pagesSEGMENT15 Predicated IndirectryujindanceNo ratings yet

- Ss8.Iterative CircuitsDocument33 pagesSs8.Iterative CircuitsryujindanceNo ratings yet

- B Logic Part1.2023Document67 pagesB Logic Part1.2023ryujindanceNo ratings yet

- Brosur Accsess Control - HoneywellDocument4 pagesBrosur Accsess Control - HoneywellrizkyNo ratings yet

- Message Reference Volume 2Document639 pagesMessage Reference Volume 2BalazsPeterNo ratings yet

- Manual BasecamDocument118 pagesManual BasecamGermán BergerNo ratings yet

- HD-3568S Specification V2.2Document24 pagesHD-3568S Specification V2.2soporteNo ratings yet

- 3519 AllDocument4 pages3519 AllAnikendu MaitraNo ratings yet

- The Ultimate Guide To Remote Production 1679256219Document22 pagesThe Ultimate Guide To Remote Production 1679256219Mohammed BayoumyNo ratings yet

- Datasheets/BLUE/APx4 DatasheetDocument51 pagesDatasheets/BLUE/APx4 Datasheetfoxxx666No ratings yet

- Fundamentals of Information Systems, Seventh EditionDocument86 pagesFundamentals of Information Systems, Seventh EditionTawanda MahereNo ratings yet

- HNC Servo manual - Tài liệu về servo HNCDocument83 pagesHNC Servo manual - Tài liệu về servo HNCNguyễn Văn DũngNo ratings yet

- Whatis Techtarget Mobile SecurityDocument3 pagesWhatis Techtarget Mobile Securitydevid mandefroNo ratings yet

- Hvacbms 190214045355Document57 pagesHvacbms 190214045355kksajjanamNo ratings yet

- 10Gbps XFP Optical Transceiver: RTXM226-405Document8 pages10Gbps XFP Optical Transceiver: RTXM226-405Lerner MapurungaNo ratings yet

- p59 0x0a Execution Path Analysis Finding Kernel Rootkits by J.K.rutkowskiDocument22 pagesp59 0x0a Execution Path Analysis Finding Kernel Rootkits by J.K.rutkowskiabuadzkasalafyNo ratings yet

- Mc1495datasheet 3609985603Document16 pagesMc1495datasheet 3609985603pepenitoNo ratings yet

- Java Theory AnswersDocument20 pagesJava Theory AnswersGaurav GaikwadNo ratings yet

- Plcopen: Iec 61131-3: A Standard Programming ResourceDocument4 pagesPlcopen: Iec 61131-3: A Standard Programming ResourceChaitanya KumarNo ratings yet

- Multi Threshold (MVT) Voltage TechniqueDocument4 pagesMulti Threshold (MVT) Voltage TechniquesunnygogineniNo ratings yet

- Unit 1 AssignmentDocument2 pagesUnit 1 AssignmentYash PatilNo ratings yet

- C232ch4 - Platform TuningDocument6 pagesC232ch4 - Platform TuningRodrigo SampaioNo ratings yet

- SDA-2400 Owners Manual - 03-11-2015 PDFDocument17 pagesSDA-2400 Owners Manual - 03-11-2015 PDF692265No ratings yet

- Imxtflug: I.Mx Tensorflow Lite On Android User'S GuideDocument42 pagesImxtflug: I.Mx Tensorflow Lite On Android User'S GuideFernando CisnerosNo ratings yet

- Emailing Lyla B DasDocument378 pagesEmailing Lyla B DasNotes50% (2)

- Certified Electronic Voting Systems As of Dec. 7, 2021 Meeting - 2021-12-21 (CURRENT)Document2 pagesCertified Electronic Voting Systems As of Dec. 7, 2021 Meeting - 2021-12-21 (CURRENT)Trent BakerNo ratings yet

- OJO Terminales 80x8Document23 pagesOJO Terminales 80x8Jonathan Alberto Osorio BenitezNo ratings yet

- AppletDocument31 pagesAppletSumanthReddyNo ratings yet

- Pink Python ArabicDocument330 pagesPink Python Arabical3meed33No ratings yet

- Alarm AnnunciatorsDocument11 pagesAlarm AnnunciatorsbhaveshbhoiNo ratings yet

Lecture 5a Pipelining

Lecture 5a Pipelining

Uploaded by

ryujindance0 ratings0% found this document useful (0 votes)

4 views21 pagesCopyright

© © All Rights Reserved

Available Formats

PPT, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PPT, PDF, TXT or read online from Scribd

Download as ppt, pdf, or txt

0 ratings0% found this document useful (0 votes)

4 views21 pagesLecture 5a Pipelining

Lecture 5a Pipelining

Uploaded by

ryujindanceCopyright:

© All Rights Reserved

Available Formats

Download as PPT, PDF, TXT or read online from Scribd

Download as ppt, pdf, or txt

You are on page 1of 21

Pipelining

(based on slides by Patricia

Brenztejn, Univ. of Buenos Aires)

Overview

• We will discuss as an example a

summation of two 128-bit numbers

• We will look at three solutions:

– simple (combinational)

– sequential

– pipelined

• We will analyze the advantages and

disadvantages of each

Combinational summation

Cost and Time of Combinational

summation

• Cost is simply four 32-bit adders and four 32-bit

registers at the output if we want to register the

result (and we probably do)

• Latency is 4 times the delay of a 32 bit adder

plus one TFF

• We can reduce the overall latency by using

lookahead logic, but that will increase the logic

cost. We won’t do this here in order to have a

good comparison with the other architectures.

Combinational Summation: Cost in

resources (C) and cost in Time (T)

• The cost in logic is (assuming output register):

C=128CFF+4Cadder(32)

• The cost in time (time per result, or 1/throughput, in this

case equal to the minimum clock period) is:

Tmin>TFF+4*Tadder(32)

• Note that TFF is defined as the summation of both setup

time and clk-to-q delay of the flip-flops

Sequential Summation (not

pipelining)

• Suppose that we want to implement a 128-bit

adder using a 32-bit summer.

• This is a sequential implementation, i.e. we will

reuse the 32-bit adder four times in order to get

the 128-bit sum

• Though it may not make sense to do this for

addition, this is an example of reusing a

resource in the chip to save logic area, at the

expense of latency. This is done a lot for more

complicated blocks (e.g. FFT).

• To determine the number of clock cycles

necessary we can make a flow diagram.

Sequential Addition

Sequential Addition: Resources

• We will need four 32-bit registers in order

to store the result of each cycle, and

another flip-flop for the carry out.

• It will take at least 4 clock cycles to

complete a 128-bit sum

Sequential addition:

Implementation

Sequential Addition: Cost in

resources (C) and cost in Time (T)

• Cost in resources can be show to be:

• Cost in time (time per result, or

1/throughput) can be shown to be:

Necessity of control FSM

• To implement the sequential addition, we need to

have a state machine that will manipulate the

control signals in the sequential adder circuit.

• The state machine will be easy to visualize

(simple linear flowchart) but this is only true in

relatively simple cases such as this adder

• The FSM incurs an additional (small) resource

cost and potentially an additional small delay as

well (usually of one or two cycles)

Implementation via Pipeline

• We talked about pipelining earlier

• Basically the idea is to separate the

operation into smaller parts that can

operate faster than the whole design

• In this case, for a fair comparison let’s

separate into 4 pipeline stages, each of

which will sum 32 bits

• As we saw in an earlier lecture, dividing

the operation into parts of equal latency

gets the best improvement.

Reminder: the basic idea

Productivity of Non-Pipelined

Washing/Drying/Folding Algorithm

• If each step takes 20 minutes, then the

three steps in sequence take 60 minutes,

• Therefore the throughput is 1 load every

60 minutes or 1/60 loads/minute

Productivity of Pipelined

Washing/Drying/Folding Algorithm

• If we process k loads, then this will take 40+20k minutes.

• The productivity will therefore be k/(40+20k)

loads/minute.

• Assume that k is large (nearly always the case in

hardware, since we process a lot of data), then in the

limit the productivity is 1/20, or 3 times higher than that

of the non-pipelined solution, as expected

• In general the ideal speedup is M times the non-

pipelined speed, where M is the number of stages, if the

non-pipelined logic can be divided into M equal-latency

parts. For the washing/drying/folding example, M=3. For

the 128-bit adder, M=4.

Implementation of the Pipelined

Solution

• Let’s start off from the combinational

version:

Let’s add pipeline registers…

:Notice the register widths

Cost in Time and Logic for Pipeline

Solution

• The cost in logic is :

C=708CFF+4Cadder(32)

• The cost in time (minimum clock period,

1/throughput) is:

Tmin>TFF+Tadder(32)

• Note the huge increase in FFs, and the big

speedup, both as expected

Comparison/Conclusions

• Sequential implementation used the least

adders. If this were a very complicated function

(e.g. FFT), this may have been a very big

advantage. However it had the longest latency.

• Combinational implementation (+ output flip-

flops) used a low amount of resources, but long

latency rivaling that of the sequential solution.

• Pipelining solution was much faster but required

a lot more flip-flops.

• Conclusion: if we want to do something really

fast, pipelining is a good option, but we must

have the necessary logic resources.

Pipelining In-Class Activity

• In the In-Class Activity we will do exactly

what we talked about in this lecture

• We will construct a 128-bit adder, first

combinationally and then using pipelining

• We will use timing analyzer to analyze and

compare the results

• We will thus get practice in actual pipeline

design and we will observe first-hand the

speedup achievable.

You might also like

- Dell Color Laser Printer 2155CN Parts Service Manual PDFDocument1,048 pagesDell Color Laser Printer 2155CN Parts Service Manual PDFlmsserviceNo ratings yet

- Calix C7 R8.0 Provisioning GuideDocument586 pagesCalix C7 R8.0 Provisioning GuideKevin Upchurch100% (1)

- DDMDocument4 pagesDDMsengottaiyan100% (4)

- Assignment 1Document2 pagesAssignment 1Samira YomiNo ratings yet

- Pipelining Size and DepthDocument19 pagesPipelining Size and Depthwardabibi69No ratings yet

- Module 4Document12 pagesModule 4Bijay NagNo ratings yet

- Multipath 1 NotesDocument37 pagesMultipath 1 NotesNarender KumarNo ratings yet

- ILP - Appendix C PDFDocument52 pagesILP - Appendix C PDFDhananjay JahagirdarNo ratings yet

- CO2202 L14 CacheDocument31 pagesCO2202 L14 Cachevidsa2002No ratings yet

- 4-2 & 5-2 CompresorDocument20 pages4-2 & 5-2 CompresorJason MillerNo ratings yet

- Chapter 9 - Pipeline and Vector Processing Section 9.1 - Parallel ProcessingDocument10 pagesChapter 9 - Pipeline and Vector Processing Section 9.1 - Parallel Processingrajput12345No ratings yet

- Pipeline Processing CoaDocument34 pagesPipeline Processing Coahagos abateNo ratings yet

- Unit 4 - P 2Document13 pagesUnit 4 - P 2Sanju SanjayNo ratings yet

- Ovn MainDocument54 pagesOvn MainAvenir BajraktariNo ratings yet

- Operating Sytems: B.Tech Ii Yr (Term 08-09) Unit 2 PPT Slides Text BooksDocument52 pagesOperating Sytems: B.Tech Ii Yr (Term 08-09) Unit 2 PPT Slides Text BooksGopal KarmakarNo ratings yet

- Appendix ADocument93 pagesAppendix AzeewoxNo ratings yet

- Analytical Modeling of Parallel Systems: Ananth Grama, Anshul Gupta, George Karypis, and Vipin KumarDocument67 pagesAnalytical Modeling of Parallel Systems: Ananth Grama, Anshul Gupta, George Karypis, and Vipin KumarzoravarNo ratings yet

- Coa Module 3 Part 1Document42 pagesCoa Module 3 Part 1Ajith Bobby RajagiriNo ratings yet

- Exercise 4Document4 pagesExercise 4Mashavia AhmadNo ratings yet

- OOADDocument67 pagesOOADBobby JasujaNo ratings yet

- PipeliningDocument12 pagesPipeliningAradhyaNo ratings yet

- Project Review: by Vamsikrishna Chemudupati 14BEC0022Document35 pagesProject Review: by Vamsikrishna Chemudupati 14BEC0022VAMSIKRISHNA CHEMUDUPATI 14BEC0022No ratings yet

- Aca Module 2Document35 pagesAca Module 2Shiva prasad100% (1)

- Embedded Systems Design: Pipelining and Instruction SchedulingDocument48 pagesEmbedded Systems Design: Pipelining and Instruction SchedulingMisbah Sajid ChaudhryNo ratings yet

- 07 RTL Optimization TechniquesDocument20 pages07 RTL Optimization Techniquesgideontargrave7No ratings yet

- C F C P S (CS61063) : Tutorial 1Document13 pagesC F C P S (CS61063) : Tutorial 1brahma2deen2chaudharNo ratings yet

- Advance Electronics: UnacademyDocument38 pagesAdvance Electronics: UnacademyhemuNo ratings yet

- Pipelining: Advanced Computer ArchitectureDocument30 pagesPipelining: Advanced Computer ArchitectureShinisg Vava100% (1)

- Bash Course - Tutorial 4: Simulation Runtime ResultsDocument1 pageBash Course - Tutorial 4: Simulation Runtime Resultsanidcohen9058No ratings yet

- M116C 1 M116C 1 Lect02-PerformanceDocument23 pagesM116C 1 M116C 1 Lect02-PerformancetinhtrilacNo ratings yet

- Pipeline and Vector ProcessingDocument28 pagesPipeline and Vector ProcessingTerror BladeNo ratings yet

- Unit-V NEWDocument21 pagesUnit-V NEWsandhya vaniNo ratings yet

- Complexity Analysis Time-Space Trade-OffDocument51 pagesComplexity Analysis Time-Space Trade-OffJatin SinghNo ratings yet

- "Iron Law" of Processor Performance: Prof. R. Iris Bahar EN164 January 31, 2007Document4 pages"Iron Law" of Processor Performance: Prof. R. Iris Bahar EN164 January 31, 2007Charan Pratap SinghNo ratings yet

- Unit-4 Pipelinie and Vector ProcessingDocument33 pagesUnit-4 Pipelinie and Vector ProcessingMandeepNo ratings yet

- Parallel Computing Platforms: Chieh-Sen (Jason) HuangDocument21 pagesParallel Computing Platforms: Chieh-Sen (Jason) HuangBalakrishNo ratings yet

- Lecture: Pipelining BasicsDocument28 pagesLecture: Pipelining BasicsTahsin Arik TusanNo ratings yet

- Stud CSA Mod 5p2 Arithmetic SuperPipelineDocument57 pagesStud CSA Mod 5p2 Arithmetic SuperPipelinesheenaneesNo ratings yet

- Unit 5Document61 pagesUnit 5prototypes6341No ratings yet

- Pipelining: Basic and Intermediate ConceptsDocument69 pagesPipelining: Basic and Intermediate ConceptsmanibrarNo ratings yet

- Lecture 3: Performance/Power, MIPS InstructionsDocument18 pagesLecture 3: Performance/Power, MIPS Instructionskotewed571No ratings yet

- Pipeline ProcessingDocument28 pagesPipeline Processinganismitaray14No ratings yet

- 7th Sem Cim Module-III 3.2Document19 pages7th Sem Cim Module-III 3.2Abdul GaffarNo ratings yet

- 4 Instruction Set ArchitecturesDocument20 pages4 Instruction Set Architectures'Joenabie Maxey GamaoNo ratings yet

- DSP Architecture - Part 1Document36 pagesDSP Architecture - Part 1Sarabjeet SinghNo ratings yet

- CSO Computer ProgrammingDocument73 pagesCSO Computer ProgrammingAjNo ratings yet

- Exercise 3 & 12Document17 pagesExercise 3 & 12perreiragabriel172No ratings yet

- 3 Process SchedulingDocument18 pages3 Process Schedulingmoin latifNo ratings yet

- Transport Control Protocol: OutlineDocument18 pagesTransport Control Protocol: OutlineSaranya BaskaranNo ratings yet

- CS-20002 (Os) - CS End April 2024Document13 pagesCS-20002 (Os) - CS End April 2024Shradha SwarupNo ratings yet

- Uni1-2 PipeliningDocument12 pagesUni1-2 PipeliningAditi VermaNo ratings yet

- Parallel Programming: in C With Mpi and Openmp Michael J. QuinnDocument73 pagesParallel Programming: in C With Mpi and Openmp Michael J. QuinnRohan PatilNo ratings yet

- 3 Process SchedulingDocument48 pages3 Process SchedulingAmit KumarNo ratings yet

- Lecture 3: Performance/Power, MIPS InstructionsDocument22 pagesLecture 3: Performance/Power, MIPS InstructionsHariharan SNo ratings yet

- A Scalable Approximate DCT Architecture For Efficient Hevc Compliant Video CodingDocument13 pagesA Scalable Approximate DCT Architecture For Efficient Hevc Compliant Video CodingvickyNo ratings yet

- Embedded Lecture 4 ARMDocument47 pagesEmbedded Lecture 4 ARMmsmukeshsinghmsNo ratings yet

- Hardware Realisation of A Computer System: Architecting SpeedDocument18 pagesHardware Realisation of A Computer System: Architecting SpeedMandy LoresNo ratings yet

- Mod6 2 PDFDocument15 pagesMod6 2 PDFsourav giriNo ratings yet

- HSE-3 Soc Chip Basics - ClearDocument50 pagesHSE-3 Soc Chip Basics - ClearUdayaJasperNo ratings yet

- Unit-5 (Coa) NotesDocument33 pagesUnit-5 (Coa) NotesyashNo ratings yet

- Numerical Methods for Simulation and Optimization of Piecewise Deterministic Markov Processes: Application to ReliabilityFrom EverandNumerical Methods for Simulation and Optimization of Piecewise Deterministic Markov Processes: Application to ReliabilityNo ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- Additional Problems 8Document2 pagesAdditional Problems 8ryujindanceNo ratings yet

- Additional Problems 6Document2 pagesAdditional Problems 6ryujindanceNo ratings yet

- Lecture 3b Verilog FSM ExamplesDocument19 pagesLecture 3b Verilog FSM ExamplesryujindanceNo ratings yet

- Module U3 - Risk Management V2Document12 pagesModule U3 - Risk Management V2ryujindanceNo ratings yet

- SEGMENT16 Switch StatementsDocument17 pagesSEGMENT16 Switch StatementsryujindanceNo ratings yet

- SEGMENT15 Predicated IndirectDocument5 pagesSEGMENT15 Predicated IndirectryujindanceNo ratings yet

- Ss8.Iterative CircuitsDocument33 pagesSs8.Iterative CircuitsryujindanceNo ratings yet

- B Logic Part1.2023Document67 pagesB Logic Part1.2023ryujindanceNo ratings yet

- Brosur Accsess Control - HoneywellDocument4 pagesBrosur Accsess Control - HoneywellrizkyNo ratings yet

- Message Reference Volume 2Document639 pagesMessage Reference Volume 2BalazsPeterNo ratings yet

- Manual BasecamDocument118 pagesManual BasecamGermán BergerNo ratings yet

- HD-3568S Specification V2.2Document24 pagesHD-3568S Specification V2.2soporteNo ratings yet

- 3519 AllDocument4 pages3519 AllAnikendu MaitraNo ratings yet

- The Ultimate Guide To Remote Production 1679256219Document22 pagesThe Ultimate Guide To Remote Production 1679256219Mohammed BayoumyNo ratings yet

- Datasheets/BLUE/APx4 DatasheetDocument51 pagesDatasheets/BLUE/APx4 Datasheetfoxxx666No ratings yet

- Fundamentals of Information Systems, Seventh EditionDocument86 pagesFundamentals of Information Systems, Seventh EditionTawanda MahereNo ratings yet

- HNC Servo manual - Tài liệu về servo HNCDocument83 pagesHNC Servo manual - Tài liệu về servo HNCNguyễn Văn DũngNo ratings yet

- Whatis Techtarget Mobile SecurityDocument3 pagesWhatis Techtarget Mobile Securitydevid mandefroNo ratings yet

- Hvacbms 190214045355Document57 pagesHvacbms 190214045355kksajjanamNo ratings yet

- 10Gbps XFP Optical Transceiver: RTXM226-405Document8 pages10Gbps XFP Optical Transceiver: RTXM226-405Lerner MapurungaNo ratings yet

- p59 0x0a Execution Path Analysis Finding Kernel Rootkits by J.K.rutkowskiDocument22 pagesp59 0x0a Execution Path Analysis Finding Kernel Rootkits by J.K.rutkowskiabuadzkasalafyNo ratings yet

- Mc1495datasheet 3609985603Document16 pagesMc1495datasheet 3609985603pepenitoNo ratings yet

- Java Theory AnswersDocument20 pagesJava Theory AnswersGaurav GaikwadNo ratings yet

- Plcopen: Iec 61131-3: A Standard Programming ResourceDocument4 pagesPlcopen: Iec 61131-3: A Standard Programming ResourceChaitanya KumarNo ratings yet

- Multi Threshold (MVT) Voltage TechniqueDocument4 pagesMulti Threshold (MVT) Voltage TechniquesunnygogineniNo ratings yet

- Unit 1 AssignmentDocument2 pagesUnit 1 AssignmentYash PatilNo ratings yet

- C232ch4 - Platform TuningDocument6 pagesC232ch4 - Platform TuningRodrigo SampaioNo ratings yet

- SDA-2400 Owners Manual - 03-11-2015 PDFDocument17 pagesSDA-2400 Owners Manual - 03-11-2015 PDF692265No ratings yet

- Imxtflug: I.Mx Tensorflow Lite On Android User'S GuideDocument42 pagesImxtflug: I.Mx Tensorflow Lite On Android User'S GuideFernando CisnerosNo ratings yet

- Emailing Lyla B DasDocument378 pagesEmailing Lyla B DasNotes50% (2)

- Certified Electronic Voting Systems As of Dec. 7, 2021 Meeting - 2021-12-21 (CURRENT)Document2 pagesCertified Electronic Voting Systems As of Dec. 7, 2021 Meeting - 2021-12-21 (CURRENT)Trent BakerNo ratings yet

- OJO Terminales 80x8Document23 pagesOJO Terminales 80x8Jonathan Alberto Osorio BenitezNo ratings yet

- AppletDocument31 pagesAppletSumanthReddyNo ratings yet

- Pink Python ArabicDocument330 pagesPink Python Arabical3meed33No ratings yet

- Alarm AnnunciatorsDocument11 pagesAlarm AnnunciatorsbhaveshbhoiNo ratings yet