Professional Documents

Culture Documents

CH 2

CH 2

Uploaded by

sp64450220 ratings0% found this document useful (0 votes)

3 views24 pagesOriginal Title

ch2 (1)

Copyright

© © All Rights Reserved

Available Formats

PPTX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PPTX, PDF, TXT or read online from Scribd

Download as pptx, pdf, or txt

0 ratings0% found this document useful (0 votes)

3 views24 pagesCH 2

CH 2

Uploaded by

sp6445022Copyright:

© All Rights Reserved

Available Formats

Download as PPTX, PDF, TXT or read online from Scribd

Download as pptx, pdf, or txt

You are on page 1of 24

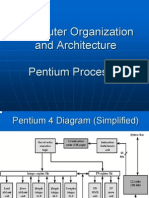

Introduction to Pentium

Processor

Marks 32

Visit for more Learning Resources

Features of Pentium Processor

• Separate instruction and Data caches.

• Dual integer pipelines i.e. U-pipeline and V-

Pipeline.

• Branch prediction using the branch target buffer

(BTB).

• Pipeliened floating point unit.

• 64- bit external data bus.

• Even-parity checking is implemented for data

bus, caches and TLBs.

Salient Features

• 32- bit Superscalar and super-pipelined

architecture CISC processor.

• 32-bit address bus can address up to 4GB of

physical memory.

• 64- bit data bus so arithmetic and logical

operation can be perform on 64-bit operand.

• Two integer pipeline U and V with two ALU’s

provide one-clock execution for core instructions

which Improved Instructions to execute Time.

• Support five stage pipeline enables multiple

instructions to execute in parallel with high

efficiency.

• Two 8 KB caches memories, one for data and

other for code.

• On- chip pipelined floating point coprocessor.

• Support power management feature i.e. System

Management mode and Clock Control.

• Enhanced branch prediction buffer.

• On-chip memory management unit.

• Support multiprogramming and multitasking.

• Internal error Detection features.

• 4MB pages for increased TLB Hit Rate.

• Support for Second level cache and Write Back

MESI.

• Protocol in the data cache.

• Supports Bus cycle Pipelining, Address Parity

and Internal Parity Checking, Functional

Redundancy checking, Execution Tracing,

Performance Monitoring.

Superscalar Execution

• It supports superscalar pipeline architecture.

• The Pentium processor sends two instructions

in parallel to the two independent integer

pipeline known as U and V pipelines for

execution of multiple instructions

concurrently.

• Thus, processor capable of parallel instruction

execution of multiple instructions is known as

Superscalar Machine.

• Each of these pipeline i.e. U and V, has 65

stages of execution i.e.

– Prefetch

– First Decode

– Second Decode

– Execute

– Write Back

1. Pre-fetch (PF): In this stage, instructions are

prefetched by prefetch buffer through U and

V pipelene from the on-chip instruction

cache.

2. First Decode (D1): In this stage, two decoders

decode the instructions to generate a control

word and try to pair them together so they

can run in parallel.

3. Second Decode (D2): In this stage, the CPU

decodes the control word and calculates the

address of memory operand.

4. Execute (EX): The instruction is executrd in

ALU and data cache is accessed at this stage.

For both ALU and data cache access requires

more than one clock.

5. Write Back (WB): In this stage, the CPU stores

result and update the flags.

Separate Code and Data Caches:

• Pentium has two separate 8KB caches for code and

data as the superscalar design and branch prediction

need more bandwidth than a unified cache.

• The data cache has a dedicated TLB to translate linear

address into physical address used by data cache.

• The code cache is responsible for getting raw

instructions into execution unis of the Pentium

processor and hence instructions are fetched from the

code cache.

Advantages of having Separate Code and

Data Caches

• Separate caches efficiently execute the branch prediction.

• Caches raise system performance i.e. an internal read

request is performed more quickly than a bus cycle to

memory.

• Separate caches also reduce the processor’s use of the

external bus when the same location are accessed multiple

times.

• Separate caches for instructions a and data allow

simultaneous cache look-up.

• Up to two data references and up to 32 bytes of raw op-

codes can be accessed In one clock.

Branch Prediction

• Branch prediction is used to predict the most likely

set of instruction to be executed and prefetch to

make them available to the pipeline as and when they

are called.

• Hence the pentium processor incorporate a branch

target buffer (BTB), which is an associative memory

used to improve the performance if it takes the

branch instrction.

• Branch instructions of pentium processor change the

normal sequential control flow of the program

execution and may stall the pipelined execution in the

pentium system.

• Branches instruction is of two types i.e. conditional

and unconditional branch.

• During the conditional branching, the CPU has two

wait till the execution stage to determine whether

the condition is satisfied or not.

• When the condition satisfies, a branching is to be

taken using branch prediction algorithm for speed up

of the instruction execution.

• In pentium Processor, BTB can have 256 entries which

contains the branch target address for previously

executed branches.

• The BTB is four ways set associative on-chip memory.

• Whenever the branching occurs, the CPU checks the branch

instruction address and the destination address in the BTB.

• When the instruction is decoded, the CPU searches the

branch target buffer to decide whether any entry exists for

a corresponding branch instruction.

• If BTB is hit, i.e. if BTB exist such entries, then the CPU use

the history to decide whether the branch will be taken or

not.

• If the entry exist in its previous history in BTB to take the

branch, the CPU fetches the instruction from the target

address and decodes them.

• If the branch prediction is correct, the process continue

else the CPU clears the pipeline and fetches from the

appropriate target address.

Floating point Unit

• The Pentium contains an on chip floating point

unit that provides significant floating point

performance advantage over previous

generations of processors.

• Providing the coprocessor onto the same chip

as the processor, pentium allows faster

communication and quicker execution.

• Thus many floating point instructions requires

fewer clock cycles that the previous 80X87.

Floating Point Pipeline

• The floating point pipeline of Pentium consists of eight

stages which are used to speedup the execution of

floating point unit. Hence, it is necessary floating point

pipeline.

• These are prefetch, first decode, second decode,

operand fetch, first execute, second execute, write float

and error reporting.

• Floating point unit has eight stage pipeline which gives a

single cycle execution for many of floating point

instructions such as floating adds, subtract, multiply and

compare

• The stages and their functions are given below:

1. PF: Instructions are prefetched from the on chip

instruction cache.

2. D1: Instruction decode to generate control word. A

single control word causes direct execution of an

instruction and complex instruction require micro-

coded control sequence.

3. D2: Address of memory resident operand are

calculated.

4. Ex: In this stage, register read, memory read or

memory write operation is performed to access an

operand as required by the instructioin.

5. X1: In this stage, the floating point data from register

or memory is written into floating point register or

memory is written into floating point register and

converted to floating point format before loaded into

the floating point unit.

6. X2: In this stage, the floating point operation is

performed by floating point unit.

7. WF: In this stage, results or floating point operation

are rounded and the written to the destination

floating point register.

8. ER: In this stage, if any error is occurred during

floating point execution, then it is reported and FPU

status word is updated.

Floating point Exception

• There are six floating point exception condition while

execution floating point instructions are available in

status word register of Pentium FPU.

• These exceptions are:

1. Invalid Opeartions:

– Stack overflow or underflow

– Invalid arithmatic operation

This exception occurs when stack fault flag (SF) of the FPU

status word indicates the type of operation i.e. stack overflow

or Underflow for SF=1 and an arithmetic instruction has

encountered an invalid operand for SF=1.

• Divide by zero: This exception occurs wheneveran

instruction attempts to divid a finite non-zero operand by 0.

• De-normalized operand exception: The de-normal operand

exception occurs if an arithmetic instruction attempts to

operate on a de-normal operand or if an attempt is made to

load de-normal single or double real value into an FPU

register.

• Numeric flow exception: This exception occurs whenever

the rounded result of an arithmetic instruction is less than

the smallest possible normalized, finite value that will fit

into the real format of the destination operand.

• Inexact result (Precision) Exception: This exception occurs if

the result of an operation is not exactly representable in the

destination format.

Comparison of 80386 and Pentium

80386 Pentium

32- bit integer core CPU with 32 bit Data 32 bit CPU with 64-bit data bus

bus

No superscalar architecture and single Superscalar architecture i.e. two pipelined

cycle execution Integer Units are capable of 2 Instructions

per clock

Ni internal cache available for data and Separate 8KB code and 8KB data cache

code available

80386 does not support branch prediction Advanced design feature i.e. Dynamic

branch Prediction

One integer Alu Two integer ALU

Operating frequency are 20 MHz to 66 Operating frequency 60 MHz and more

MHz

FPU is non- pipelined as it is an external FPU is pipelined as it is in built in pentium

device 80387

Pentium Pro Features

• The Pentium pro has a performance near about 50%

higher than a Pentium of the same clock speed.

• Super-pipelining: 14 stages pipelining as compare to 5

stage of pentium Processor.

• Integrated Level 2 Cache: 256-KB static Ram on- chip

coupled to the core processor through a full clock speed,

64- bit, cache bus.

• 32- bit Optimization: Optimized for running, 32-bit code

used in Windows NT.

• Wider Address Bus: 36 bit address bus which is used to

address 236=64GB of physical address space.

• Greater Multiprocessing: Multi-processor systems of up to 4

Pentium Pro processors.

• Out of order completion: Out of order execution mechanism

called as dynamic execution.

• Superior branch prediction Unit: The branch target buffer (BTB)

is double the size as compare to Pentium processor which

increases its accuracy.

• Register renaming: Improves parallel performance of the

pipelines.

• Speculative execution: Speculative execution reduces pipeline

stall time in its RISC core.

• Dynamic data flow analysis: Real time analysis of the flow of

data trough the processor to determine data and register

dependencies and to detect opportunities for out of order

instruction execution.

For more detail contact us

You might also like

- Free Ebook To Learn and Design Your Own Microcontroller ProjectsDocument111 pagesFree Ebook To Learn and Design Your Own Microcontroller ProjectsAjay BharatiyaNo ratings yet

- Cse PSG Semester 1Document77 pagesCse PSG Semester 1Hari HrithikNo ratings yet

- Module 5 - Pentium Processors - FinalDocument43 pagesModule 5 - Pentium Processors - FinalKEVINNo ratings yet

- Intel 80586 (Pentium)Document24 pagesIntel 80586 (Pentium)Soumya Ranjan PandaNo ratings yet

- 5.1 Pentiun ArchitectureDocument10 pages5.1 Pentiun Architecturenehareddy.alla17No ratings yet

- PentiumDocument18 pagesPentiumJain Marshel BNo ratings yet

- Basicfeaturesof Advanced MicroprocessorsDocument15 pagesBasicfeaturesof Advanced MicroprocessorsAMISHANo ratings yet

- ArchitectureDocument14 pagesArchitectureGopal PawarNo ratings yet

- Module 4 MPDocument11 pagesModule 4 MPvreshmi885113No ratings yet

- Cpe 631 Pentium 4Document111 pagesCpe 631 Pentium 4rohitkotaNo ratings yet

- Pentium - Salient FeaturesDocument16 pagesPentium - Salient Featuressantosh.parsaNo ratings yet

- Pentium-4 RNM FinalDocument27 pagesPentium-4 RNM FinalRajNo ratings yet

- Instruction Level ParallelismDocument49 pagesInstruction Level ParallelismBijay MishraNo ratings yet

- Pentium 4 Pipe LiningDocument7 pagesPentium 4 Pipe Liningapi-3801329100% (5)

- Amp Units 3&4 NotesDocument18 pagesAmp Units 3&4 NotesSumithNo ratings yet

- Pentium 4 StructureDocument38 pagesPentium 4 Structureapi-3801329100% (6)

- Computer Organization Unit-Iv (V) Computer System DesignDocument15 pagesComputer Organization Unit-Iv (V) Computer System DesignShudhodhan BokefodeNo ratings yet

- Pic 16F877Document115 pagesPic 16F877narendramaharana39100% (1)

- Pentium ArchitectureDocument3 pagesPentium ArchitectureweblnsNo ratings yet

- Task Switching:: JMP Call JMP Call Iret JMP Call IretDocument19 pagesTask Switching:: JMP Call JMP Call Iret JMP Call IretAshish PatilNo ratings yet

- Processor OrganizationDocument55 pagesProcessor OrganizationMinoshini Fonseka100% (1)

- Pentium ArchitectureDocument3 pagesPentium ArchitecturedeapaNo ratings yet

- MP - Module 6 - Pentium 4 - Aeraxia - inDocument6 pagesMP - Module 6 - Pentium 4 - Aeraxia - inraunakgond29No ratings yet

- Advanced MicroprocessorsDocument20 pagesAdvanced Microprocessorsprakash_oxfordNo ratings yet

- Chapter 2 Part FourDocument76 pagesChapter 2 Part FoursileNo ratings yet

- ED Unit-1Document83 pagesED Unit-1Brij Nandan SinghNo ratings yet

- Instruction PipelineDocument27 pagesInstruction PipelineEswin AngelNo ratings yet

- 5.3 Integer and Floating Point Pipeline StagesDocument12 pages5.3 Integer and Floating Point Pipeline Stagesnehareddy.alla17No ratings yet

- Microprocessor ArchitectureDocument23 pagesMicroprocessor Architectureganesh6583No ratings yet

- 2-Introduction To Pentium ProcessorDocument15 pages2-Introduction To Pentium Processorafzal_a92% (13)

- Intel Pentium Pro: Presented byDocument16 pagesIntel Pentium Pro: Presented byIan John MontalboNo ratings yet

- ARM ProcessorDocument46 pagesARM Processoryixexi7070No ratings yet

- Power PC ArchitectureDocument28 pagesPower PC ArchitecturedesamratNo ratings yet

- 80486Document21 pages80486Khadar Nawas0% (1)

- Pin Diagram of PENTIUM MicroprocessorDocument22 pagesPin Diagram of PENTIUM MicroprocessorNithyakumar Mohanasundaram67% (3)

- Folien Intel NetBurst ArchitectureDocument7 pagesFolien Intel NetBurst ArchitectureHawx GamerNo ratings yet

- ARM 1vDocument31 pagesARM 1vsuntosh_14No ratings yet

- 15CS205J-Microprocessors and Microcontrollers Assignment: Pentium ProDocument7 pages15CS205J-Microprocessors and Microcontrollers Assignment: Pentium ProManpreetNo ratings yet

- 12 - Processor Structure and FunctionDocument73 pages12 - Processor Structure and FunctionRao FaisalNo ratings yet

- CH12 CPU Structure and FunctionDocument44 pagesCH12 CPU Structure and FunctionUsha PrasannaNo ratings yet

- Module 2Document34 pagesModule 2Godwin EkanemNo ratings yet

- 2-Unit 2 MPMC 8086 NotesDocument22 pages2-Unit 2 MPMC 8086 NotesRayapati Devi Prasad100% (2)

- The Pentium Family of Processors Originated From The 80486 MicroprocessorDocument2 pagesThe Pentium Family of Processors Originated From The 80486 Microprocessorprime armyNo ratings yet

- The Intel PentiumDocument10 pagesThe Intel Pentiummani_vlsiNo ratings yet

- 6 8086 and 80286 Microprocessor - 2022 - 04may - 2022Document27 pages6 8086 and 80286 Microprocessor - 2022 - 04may - 2022patilamrutak2003No ratings yet

- 1 Adv MP Unit-IIDocument55 pages1 Adv MP Unit-IIVijayaraghavan VNo ratings yet

- Es Unit1Document83 pagesEs Unit1venneti kiranNo ratings yet

- Interfacing A Stepper Motor With ARM Controller LPC2148Document9 pagesInterfacing A Stepper Motor With ARM Controller LPC2148Rahul Sharma100% (2)

- CSC232 Chp5 Proc Design (Compatibility Mode)Document84 pagesCSC232 Chp5 Proc Design (Compatibility Mode)Hassan HassanNo ratings yet

- CPU With Systems BusDocument35 pagesCPU With Systems BusTanafe33% (3)

- # Tutorial 9 & 10Document6 pages# Tutorial 9 & 10aojiru.coNo ratings yet

- Computing Systems OrganizationDocument22 pagesComputing Systems Organizationifti_scriNo ratings yet

- Cpu 1Document6 pagesCpu 1mayan nelsonNo ratings yet

- Chapter 14 - Processor Structure and FunctionDocument74 pagesChapter 14 - Processor Structure and FunctionDeadly ChillerNo ratings yet

- PIC18 ControllerDocument60 pagesPIC18 ControllerDr Narayana Swamy RamaiahNo ratings yet

- Chap 04Document22 pagesChap 04Zerihun Bekele100% (1)

- Superscalar and Advanced Architectural Features of Powerpc and Pentium FamilyDocument11 pagesSuperscalar and Advanced Architectural Features of Powerpc and Pentium FamilyAjin AbrahamNo ratings yet

- W5 - L1 - MacInst and OperDocument36 pagesW5 - L1 - MacInst and OperNeel RavalNo ratings yet

- Embedded Microprocessor Lecture 2Document15 pagesEmbedded Microprocessor Lecture 2ojasbhosale07No ratings yet

- Instruction PipeliningDocument32 pagesInstruction PipeliningTech_MXNo ratings yet

- 8086 MicroprocessporDocument40 pages8086 MicroprocessporBiniyam LamesgenNo ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- Term 21221: Section K20RJ CSE 211: Computer Organization and Design ONLINE Assignment No.1 General InstructionsDocument4 pagesTerm 21221: Section K20RJ CSE 211: Computer Organization and Design ONLINE Assignment No.1 General InstructionsVanshX BhatiaNo ratings yet

- Lecture05 BranchesDocument47 pagesLecture05 BranchesNikitasNo ratings yet

- Implementation of Three Address CodeDocument9 pagesImplementation of Three Address CodeSbhgtvhcyNo ratings yet

- MPMC LabDocument105 pagesMPMC LabAskar AliNo ratings yet

- Lab Manual For Assembly Language CourseDocument42 pagesLab Manual For Assembly Language CourseZaid Masood KhanNo ratings yet

- CH 6 - Flow Control InstructionsDocument23 pagesCH 6 - Flow Control Instructionsapi-237335979No ratings yet

- S - C L - C++ H F T: B B P H: EMI Static Onditions in OW Latency FOR IGH Requency Rading Etter Than Ranch Rediction IntsDocument53 pagesS - C L - C++ H F T: B B P H: EMI Static Onditions in OW Latency FOR IGH Requency Rading Etter Than Ranch Rediction IntsRomuald DeleneNo ratings yet

- Chapter 8 DebuggingDocument8 pagesChapter 8 DebuggingJayesh ShindeNo ratings yet

- The Minix Assembly Language Manual: 1 CompilingDocument8 pagesThe Minix Assembly Language Manual: 1 CompilingpippoqwertyuytNo ratings yet

- ACA Assignment: Name: Anjali Singh Roll No.: 10001012017 Semester: 7th Class: CSE-2Document4 pagesACA Assignment: Name: Anjali Singh Roll No.: 10001012017 Semester: 7th Class: CSE-2Disha goyalNo ratings yet

- Unit-1 Intro To Programming - Edited PDFDocument59 pagesUnit-1 Intro To Programming - Edited PDFMark junnel NorberteNo ratings yet

- Cu 3rd SemDocument7 pagesCu 3rd SemCOMPUTER SCIENCE BGCNo ratings yet

- De&mp Unit - 5Document30 pagesDe&mp Unit - 5Mahesh BabuNo ratings yet

- Toshiba PLC V200 ManualDocument186 pagesToshiba PLC V200 ManualAnonymous aEGYwKV7lNo ratings yet

- AbbreviationsDocument194 pagesAbbreviationsJaganath HariNo ratings yet

- Types of ProcessorsDocument2 pagesTypes of Processorsadeel khanNo ratings yet

- Traditional (CISC) MachinesDocument8 pagesTraditional (CISC) MachinesDivya VijNo ratings yet

- CompArch - Chapter OneDocument9 pagesCompArch - Chapter Onegirum sisayNo ratings yet

- Assembly LanguageDocument15 pagesAssembly LanguageStephanie Bush100% (1)

- Arm Cortex M7 Processor DatasheetDocument12 pagesArm Cortex M7 Processor DatasheetAlfonso Hernández MagdalenoNo ratings yet

- Ali RasheedDocument100 pagesAli Rasheedali,r98No ratings yet

- Pic 16 F 616Document172 pagesPic 16 F 616Maneesh BakaleNo ratings yet

- Unit-4 Pipelinie and Vector ProcessingDocument33 pagesUnit-4 Pipelinie and Vector ProcessingMandeepNo ratings yet

- Concurrency in Python TutorialDocument109 pagesConcurrency in Python Tutorialswathi sree100% (1)

- GSK 988T PLC Manual (201011) 2011-01-24Document135 pagesGSK 988T PLC Manual (201011) 2011-01-24Cesar MessiasNo ratings yet

- ARM ArchitectureDocument16 pagesARM ArchitectureS S0% (1)

- Module 2: Computer-System StructuresDocument24 pagesModule 2: Computer-System StructuresViarNo ratings yet

- Exercises Assembly Language 1Document3 pagesExercises Assembly Language 1Phạm Tiến AnhNo ratings yet