Professional Documents

Culture Documents

Presentation Tanish

Presentation Tanish

Uploaded by

gcet login0 ratings0% found this document useful (0 votes)

1 views18 pagesCopyright

© © All Rights Reserved

Available Formats

PPTX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PPTX, PDF, TXT or read online from Scribd

Download as pptx, pdf, or txt

0 ratings0% found this document useful (0 votes)

1 views18 pagesPresentation Tanish

Presentation Tanish

Uploaded by

gcet loginCopyright:

© All Rights Reserved

Available Formats

Download as PPTX, PDF, TXT or read online from Scribd

Download as pptx, pdf, or txt

You are on page 1of 18

A PRESENTATION ON INTERNSHIP AT

Guided By : Prof . Rohit Parmar

Subject Name : Industrial Internship

Subject Code : 102000801

Presented By : Tanish Shah

Enroll No. : 12002060501028

Agenda

• Brief Profile of Company

• Timeline

• Verilog

• System Verilog

• Project

• Summary

Brief Profile of Company

• Headquartered in Silicon Valley, California, Scaledge has development

centers in Canada, the United Kingdom, and India. Since its inception,

Scaledge's robust team of specialists have been assisting customers in

bringing advanced products to markets quickly and efficiently.

• We specialize in developing integrated hardware and software solutions that

support the semiconductor, AI/ML, and IoT industries across many domains

such as consumer durables, storage, automotive, wireless, and data center.

• Our competence in VLSI across processors, SoCs, and sub-systems, and our

maturity in providing solutions in AI/ML and embedded software,

distinguishes us as a "Partner of Choice" for our customers.

• Our vision is to be the world’s best Technology Design Center by being the

first choice for leading companies who want to build innovative products,

and being the top choice for talents who want to steer their successful

journey for knowledge and growth.

TimeLine

January

Digital Electronics Basic Linux & GVIM

February

Verilog (Hardware Description Language)

March & April

System Verilog (Hardware Verification Language)

Verilog

Verilog HDL

Implemented Digital Circuits

Memory Design & Verification

Single Port

Real Dual Port

Dynamic Memory Controller

True Dual Port

Finite State Machine

Seq. Detector

Vending Machine

Self-Checking Test-bench

Code Coverage

Regression

Mini-Projects

Asynchronous FIFO Round Robin Arbiter

• Designed RTL • Designed RTL

• Verified Test-Cases • Verified Test-Cases

• Self-Checking Test-bench • Self-Checking Testbench

• Achieved 100% • Achieved 100%

Code Coverage Code Coverage

• Regressions • Regressions

System Verilog

Data Types

Structure & Union

Casting Object Oriented Programming concepts

Arrays

Inheritance

Static array

Dynamic array Polymorphism

Associative array

Encapsulation

Queue array

Enumeration

System Verilog

Inter Process Communication Constraint &

Mailbo Randomization

x • System Verilog allows users to specify

Event constraints in a compact, declarative

way which are then processed by an

internal solver to generate random

Semaphore values that satisfy all conditions.

SV Layered TB

APB TO I2C bridge

APB to I2C Bridge helps to communicate between two protocols i.e.,

• Advanced peripheral Bus Protocol (APB Protocol )

• Inter Integrated Communication (I2C Protocol )

Requirement of Bridge

• APB and I2C protocols works on different clock frequency.

• APB performs parallel data transfer while I2C performs serial data transfer.

Project in three phase

• APB slave RTL design and verification

• I2C master and slave RTL design and verification

• Combining both as bridge and verifying the RTL design.

Activities

1. Verilog HDL programming

• Deep learning of the hardware language.

2. Pre-requisites for the project

• APB and I2C protocol specification.

• Asynchronous FIFO design and verification.

3. APB development and verification

• APB Slave RTL design and verification.

4. SPI development and verification

• I2C Master - Slave RTL design and verification.

5. Bridge development and verification

• Combining APB Slave, I2C master and Asynchronous FIFO as Bridge.

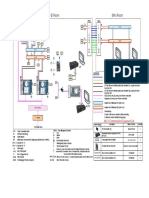

Block Diagram

FIFO Observation

APB Observation

I2C observation

Conclusion

• During the training, learned about Verilog Hardware Language and

understood concepts about the verification part in VLSI industry.

• Designing synthesizable RTL designs and further verifying them to

ensure proper working of the design.

• APB to I2C Bridge helps to perform data transfer between two protocols

working at different frequencies and working with different peripherals.

• The verification phase was crucial as it confirmed that my design is both

reliable and functional.

Q&A

$display(“Thank

you”);

You might also like

- Vlsi DesignDocument29 pagesVlsi DesigngodbhatiNo ratings yet

- Technical Content ReferenceDocument12 pagesTechnical Content ReferenceharishkecebeNo ratings yet

- Technical Content Reference - ResumeDocument8 pagesTechnical Content Reference - ResumeKiransai ReddyNo ratings yet

- Verilog CourseDocument181 pagesVerilog Coursemanya mehtaNo ratings yet

- ARM Based SoC Verification - v1Document19 pagesARM Based SoC Verification - v1Balaramkishore GangireddyNo ratings yet

- VLSI Design and VerificationDocument11 pagesVLSI Design and VerificationopenhousehereNo ratings yet

- Introduction To HDLDocument28 pagesIntroduction To HDLBack UpNo ratings yet

- VerilogDocument226 pagesVerilogNadeem AkramNo ratings yet

- Resume KumarVishalDocument4 pagesResume KumarVishalkumarvishalsingh3No ratings yet

- Vector India BrochureDocument15 pagesVector India BrochurePRAVIN GUNJALNo ratings yet

- EWAVR Introduction enDocument19 pagesEWAVR Introduction enppedro87No ratings yet

- Chapter 3 - Design and Tool FlowDocument16 pagesChapter 3 - Design and Tool FlowDanh ZEUS49No ratings yet

- F8 - Introduction To An Advanced Verification Methodology PDFDocument71 pagesF8 - Introduction To An Advanced Verification Methodology PDF陈晟音乐族--王子No ratings yet

- Subject Name: Digital System Design Course Code: IT-314Document28 pagesSubject Name: Digital System Design Course Code: IT-314Comedy Hindi HDNo ratings yet

- Resume SriSaiCherukuriDocument1 pageResume SriSaiCherukuriJalaj GuptaNo ratings yet

- Naveen Updated ResumeDocument7 pagesNaveen Updated ResumeVarun PNo ratings yet

- Resume Benazir Mustafa ASICDocument3 pagesResume Benazir Mustafa ASICShuvo BanikNo ratings yet

- 2.2 Peter SomogyvariDocument33 pages2.2 Peter Somogyvariali aghajaniNo ratings yet

- Introduction To HDLDocument72 pagesIntroduction To HDLchikku0211No ratings yet

- DSV Vip CatalogDocument4 pagesDSV Vip CatalogSamNo ratings yet

- Sample Design Verification EngineerDocument7 pagesSample Design Verification Engineervishnu microarkNo ratings yet

- Lab 1Document41 pagesLab 1J JAYDON100% (1)

- 1 Introduction To VHDL 1Document26 pages1 Introduction To VHDL 1R Venkat Kalyan NaikNo ratings yet

- Introduction To Digital SystemsDocument8 pagesIntroduction To Digital Systemsmmohammedashik2006No ratings yet

- 5164357478365108Document2 pages5164357478365108kuranggaean2No ratings yet

- VLSI Design - EDA TOOLS PDFDocument83 pagesVLSI Design - EDA TOOLS PDFprathap_somaNo ratings yet

- VLSI Design Methodology: TopicsDocument12 pagesVLSI Design Methodology: Topicskrishy19sNo ratings yet

- Lab 2Document59 pagesLab 2J JAYDONNo ratings yet

- VLSIDocument2 pagesVLSIPuneet ThakralNo ratings yet

- PDC Apr 2018 Vlsi Des VerDocument2 pagesPDC Apr 2018 Vlsi Des Verswathi bnNo ratings yet

- Sandeepani PDC VLSIDocument2 pagesSandeepani PDC VLSIAvinash BaldiNo ratings yet

- Intro To LabVIEW and Robotics Hands-On SeminarDocument58 pagesIntro To LabVIEW and Robotics Hands-On SeminarJonaHdzNo ratings yet

- Software Requirement Specification: For Voice Tree StructureDocument8 pagesSoftware Requirement Specification: For Voice Tree StructureVipin GuptaNo ratings yet

- Introduction To Digital SystemsDocument8 pagesIntroduction To Digital Systemsvickythottiyappan73No ratings yet

- Chapter 1Document38 pagesChapter 1Hamid AssadullahNo ratings yet

- Infotech Electronic Design Services OverviewDocument15 pagesInfotech Electronic Design Services OverviewVirath KaurNo ratings yet

- 04 - Introduction To VHDLDocument39 pages04 - Introduction To VHDLJorge ReyNo ratings yet

- Embedded C Programming, Linux, and Vxworks.: SynopsisDocument5 pagesEmbedded C Programming, Linux, and Vxworks.: SynopsisSwarna Sekhar Dhar100% (1)

- Manasa Hanakere Krishnappa - ResumeDocument3 pagesManasa Hanakere Krishnappa - ResumesanjuNo ratings yet

- Evolution of Digital Design and Emergence of HdlsDocument11 pagesEvolution of Digital Design and Emergence of HdlsNayanBanikNo ratings yet

- Dot NetDocument15 pagesDot Netakirank1No ratings yet

- Mahesh ShindeDocument3 pagesMahesh ShindesureshchandraNo ratings yet

- Summer Training VHDLDocument38 pagesSummer Training VHDLmjcetpaNo ratings yet

- Sachin Latest CVDocument6 pagesSachin Latest CVm.ashfaqullasharifNo ratings yet

- Software Engineering With LabVIEWDocument56 pagesSoftware Engineering With LabVIEWEngr Nayyer Nayyab MalikNo ratings yet

- Vlsi 161217161739 PDFDocument29 pagesVlsi 161217161739 PDFkondalarao79No ratings yet

- Introduction To Bare-Metal Networking: Uwe Dahlmann Iu Globalnoc Supported by NSF Eager Grant #1535522Document34 pagesIntroduction To Bare-Metal Networking: Uwe Dahlmann Iu Globalnoc Supported by NSF Eager Grant #1535522punk.tent8244No ratings yet

- Abhishek Chakraborty ResumeDocument2 pagesAbhishek Chakraborty Resumeabhi2006fiemNo ratings yet

- Oak Esbu ProfileDocument2 pagesOak Esbu ProfileSujay JoshiNo ratings yet

- Types of Modelling PDFDocument14 pagesTypes of Modelling PDFAnonymous 3XeTp7drNo ratings yet

- Ixload - Voice Test Solution: Validate That Your Voice Service Delivers A High Quality of Customer ExperienceDocument22 pagesIxload - Voice Test Solution: Validate That Your Voice Service Delivers A High Quality of Customer ExperienceBadhriNo ratings yet

- Who Am I?: Dr. Naveed Khan BalochDocument119 pagesWho Am I?: Dr. Naveed Khan Balochmr. khanNo ratings yet

- Vlsi Project Topics: Verilog Course TeamDocument4 pagesVlsi Project Topics: Verilog Course Teamverilogcourseteam0% (1)

- Verification of "Advanced Encryption Standard"Document20 pagesVerification of "Advanced Encryption Standard"nnnNo ratings yet

- CpE321L Lesson 1 - Introduction To IC Design and HDLDocument38 pagesCpE321L Lesson 1 - Introduction To IC Design and HDLSebastian KarlNo ratings yet

- Relational Database Index Design and the Optimizers: DB2, Oracle, SQL Server, et al.From EverandRelational Database Index Design and the Optimizers: DB2, Oracle, SQL Server, et al.Rating: 5 out of 5 stars5/5 (1)

- SystemVerilog for Hardware Description: RTL Design and VerificationFrom EverandSystemVerilog for Hardware Description: RTL Design and VerificationNo ratings yet

- Mastering Python Network Automation: Automating Container Orchestration, Configuration, and Networking with Terraform, Calico, HAProxy, and IstioFrom EverandMastering Python Network Automation: Automating Container Orchestration, Configuration, and Networking with Terraform, Calico, HAProxy, and IstioNo ratings yet

- Mohamed Sidan CVDocument2 pagesMohamed Sidan CVMahmoud WafaNo ratings yet

- What Is Java Technology and Why Do I Need It?Document2 pagesWhat Is Java Technology and Why Do I Need It?bigboy 4990No ratings yet

- Troubleshooting No Data Conditions On E3270ui v1.0Document17 pagesTroubleshooting No Data Conditions On E3270ui v1.0LuciaSantucciNo ratings yet

- HP ProBook 455 G4 QuickspecsDocument34 pagesHP ProBook 455 G4 QuickspecsKhushant PrakashNo ratings yet

- SPI Motorola SpecificationDocument38 pagesSPI Motorola Specificationzy798408818No ratings yet

- DVR H9106uvd SV ManualDocument38 pagesDVR H9106uvd SV ManualGuillermo ReyesNo ratings yet

- How To Use Hyper-V Snapshot Revert, Apply, and Delete OptionsDocument15 pagesHow To Use Hyper-V Snapshot Revert, Apply, and Delete OptionsKaran MishraNo ratings yet

- Selenium SyllabusDocument4 pagesSelenium SyllabusameetNo ratings yet

- DT 1.2 DivyanshuDocument11 pagesDT 1.2 DivyanshuGautam MandoliyaNo ratings yet

- Topic For The Class: Ethernet Physical Layer, Ethernet Mac Sub Layer Protocol. Date & Time: 8/02/2021Document25 pagesTopic For The Class: Ethernet Physical Layer, Ethernet Mac Sub Layer Protocol. Date & Time: 8/02/2021TomNo ratings yet

- Basic Router Configuration: 1. VerifyingDocument5 pagesBasic Router Configuration: 1. VerifyingPhoe NixNo ratings yet

- WSUS Deployment GuideDocument22 pagesWSUS Deployment GuideNobsVubaNo ratings yet

- Cometh-Field-Rd: RS232 / RS422 / RS485 DIN Rail Single Port ServerDocument2 pagesCometh-Field-Rd: RS232 / RS422 / RS485 DIN Rail Single Port ServerXaoc KabataNo ratings yet

- b0700sx F PDFDocument662 pagesb0700sx F PDFabdel taibNo ratings yet

- Programming Examples 1Document17 pagesProgramming Examples 1Dr-Amit Kumar Singh100% (1)

- R12.2 Features - MotorolaDocument56 pagesR12.2 Features - Motorolakrishanu1013No ratings yet

- 13 A - Ajnod System Configuration - HOTSTANDBYDocument1 page13 A - Ajnod System Configuration - HOTSTANDBYKrishna sesattyNo ratings yet

- Apple Inc.: 1. HistoryDocument3 pagesApple Inc.: 1. HistoryFatimah ZahraNo ratings yet

- 07 Handout 1Document3 pages07 Handout 1Bernard LunaNo ratings yet

- 2-Wire Serial EEPROM: (FeaturesDocument28 pages2-Wire Serial EEPROM: (FeaturesFernando SerratiNo ratings yet

- Installation and Administration Manual For PADS ProfessionalDocument76 pagesInstallation and Administration Manual For PADS ProfessionalLâm Lê ThanhNo ratings yet

- Configure Active Directory (AD) Synchronization For SharePoint 2010Document22 pagesConfigure Active Directory (AD) Synchronization For SharePoint 2010eleazar_lostNo ratings yet

- ASAP Utilities For Excel - Excel Shortcuts - A List of Excel's Shortcut Keys - Excel TipsDocument16 pagesASAP Utilities For Excel - Excel Shortcuts - A List of Excel's Shortcut Keys - Excel TipsAzwan AzmiNo ratings yet

- Critical Thinking Chapter 2Document3 pagesCritical Thinking Chapter 2api-346764937No ratings yet

- Computer Related Full Form Board PDFDocument9 pagesComputer Related Full Form Board PDFxsaaNo ratings yet

- Tle 9 CSS Q4 Week 5 6Document11 pagesTle 9 CSS Q4 Week 5 6Rie VisayaNo ratings yet

- CSS12Document3 pagesCSS12JERRY FLORESNo ratings yet

- CSCI 510: Computer Architecture Written Assignment 2 SolutionsDocument6 pagesCSCI 510: Computer Architecture Written Assignment 2 Solutionss_subbulakshmiNo ratings yet

- Ccs356 - Oose LabDocument138 pagesCcs356 - Oose Lab21CSE8551 NELLIYAN B.No ratings yet

- Make A Splash in LabVIEW PDFDocument17 pagesMake A Splash in LabVIEW PDFMohammad EssamNo ratings yet