Professional Documents

Culture Documents

General Register Organization

General Register Organization

Uploaded by

Shivam Sharma0 ratings0% found this document useful (0 votes)

2 views21 pagesCopyright

© © All Rights Reserved

Available Formats

PPTX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PPTX, PDF, TXT or read online from Scribd

Download as pptx, pdf, or txt

0 ratings0% found this document useful (0 votes)

2 views21 pagesGeneral Register Organization

General Register Organization

Uploaded by

Shivam SharmaCopyright:

© All Rights Reserved

Available Formats

Download as PPTX, PDF, TXT or read online from Scribd

Download as pptx, pdf, or txt

You are on page 1of 21

Ms.

Poonam Rana

Sr. Assistant Professor

ABES Engineering College, Ghaziabad

General Register Organization

ABES Engineering College, Ghaziabad. 1

In this lecture Students will be

able to learn :

Major Components of CPU

Bus Organization for seven CPU Registers

Control Word

Fields in Control Word

Encoding of Register Selection Fields

Encoding of ALU Operations

Examples of Micro-operations

Examples of Micro-operations on the CPU

ABES Engineering College, Ghaziabad. 2

Major Components of CPU:

The part of the Computer System that performs the

bulk of data processing operations is called Central

Processing Unit and is referred to as CPU.

The CPU is made up of major 3 parts:

1.Control

2. Register Set

3. Arithmetic Logic Unit.

ABES Engineering College, Ghaziabad. 3

Major Components of CPU Diagram

ABES Engineering College, Ghaziabad. 4

Functions of Major Components of CPU:

The Register set stores intermediate data used during the

execution of the instructions.

The Arithmetic logic Unit performs the required micro-

operations for executing the instructions.

The Control unit supervises the transfer of information

among the registers and instructs the ALU as to which

operation to perform.

ABES Engineering College, Ghaziabad. 5

Organization and Architecture of the CPU:

This lecture describes the organization and Architecture of

the CPU with an emphasis on the user's view of the

Computer.

In this we briefly describe how the registers communicate

with the ALU through buses .

ABES Engineering College, Ghaziabad. 6

General Register Organization

We know that memory locations are needed for storing

pointers , counters, return addresses, temporary results and

partial products during Multiplication.

Having to refer to memory locations for such applications is

time consuming because Memory access is the most time

consuming operation in a computer.

It is more convenient and more efficient to store these

intermediate values in processor registers.

When the large number of registers is included in the CPU it

is most efficient to connect them through a common bus

system.

ABES Engineering College, Ghaziabad. 7

General Register Organization:

The registers communicate with each other

not only for direct data transfers but also

while performing various micro-operations.

Hence it is necessary to provide a common

unit that perform all the arithmetic , logic and

shift micro-operations in the processor.

ABES Engineering College, Ghaziabad. 8

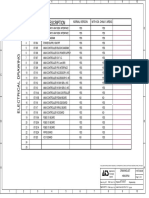

Bus Organization for 7 CPU registers:

ABES Engineering College, Ghaziabad. 9

General Register Organization

Description:

The output of each register is connected to two

multiplexers (MUX) to form the two buses A& B.

The selection lines in each Multiplexer select one

register or the input data for the particular bus

The A & B buses form the inputs to a common

arithmetic logic Unit( ALU).

ABES Engineering College, Ghaziabad. 10

General Register Organization:

The operation selected in the ALU determines the arithmetic

or logic operation that is to be performed.

The result of the micro-operation is available for output data

and also goes into the inputs of all registers.

The register that receives the information from the output

bus is selected by decoder.

The decoder activates one of the register load inputs , thus

providing a transfer path between the data in the output bus

and the inputs of the selected Destination register.

ABES Engineering College, Ghaziabad. 11

General Register Organization

The control unit that operates the CPU bus System directs

the information flow through the registers and ALU by

selecting the various components in the System. For

Example , to perform the operation.

ABES Engineering College, Ghaziabad. 12

Example of General Register

Organization

R1<-R2+R3

To Perform this operation the control unit must provide

binary variables to the following selector inputs.

a) MUX A Selector A ( SEL A) : To place the contents of R2

into BUS A.

b) MUX B Selector B(SEL B) : To place the contents of R3

INTO BUS B.

c) ALU operation selector OPR to provide the arithmetic

addition.

d) Decoder destination selector (SELD) to transfer the

content of output bus into R1.

ABES Engineering College, Ghaziabad. 13

Control Word

1. SEL A Consists of 3 bits.

2. SEL B Consists of 3 bits.

SEL A SEL B SEL D OPR

SEL D consists of 3 bits.

OPR consists of 5 bits.

ABES Engineering College, Ghaziabad. 14

Control word

There are 14 binary selection inputs in the unit, and their

combined value specifies a control word. The 14 bit control

word is defined in the previous figure.

Three fields contain three bits each and one field has five

bits.

The three bits of SEL A select a source register for the A input

of the ALU.

The three bits of SEL B selects a source register for the B

input of the ALU.

The three bits of SEL D select a destination register using the

decoder and its seven load inputs.

The five bits of OPR selects one of the operations in the ALU.

ABES Engineering College, Ghaziabad. 15

Encoding of Register Selection

fields:

Binary code SELA SEL B SEL D

000 Input Input None

001 R1 R1 R1

010 R2 R2 R2

011 R3 R3 R3

100 R4 R4 R4

101 R5 R5 R5

110 R6 R6 R6

111 R7 R7 R7

ABES Engineering College, Ghaziabad. 16

Encoding of ALU operations:

OPR select Operation Symbol

00000 Transfer A TSFA

00001 Increment A INCA

00010 Add A+B ADD

00101 Subtract A-B SUB

00110 Decrement A DECA

01000 And A and B AND

01010 OR A and B OR

01100 XOR A and B XOR

01110 Complement A COMA

10000 Shift Right A SHRA

11000 Shift Left A SHLA

ABES Engineering College, Ghaziabad. 17

Examples of Micro-operations:

R1<-R2-R3

Control word: 010 011 001 00101 for the

above micro operation .

ABES Engineering College, Ghaziabad. 18

Morris Mano Unsolved

Numerical:

A bus organized CPU has 16 registers with 32

bits in each, an ALU and a decoder.

a) How many multiplexers are there in the A

bus and What is the size of each Multiplexer?

b) How many selection inputs are needed for

MUX A and MUX B?

c) How many inputs and outputs are there in

the ALU for data, including input and output

carries?

ABES Engineering College, Ghaziabad. 19

Morris Mano Unsolved

Numerical

How many inputs and outputs are there in

the decoder?

Formulate a control word for the system

assuming that the ALU has 35 operations.

ABES Engineering College, Ghaziabad. 20

32 multiplexers, each of size 16 × 1.

(b) 4 inputs each, to select one of 16

registers.

(c) 4-to-16 – line decoder

(d) 32 + 32 + 1 = 65 data input lines

32 + 1 = 33 data output lines.

(e) 4 + 4+ 4 + 6 = 18 bits

ABES Engineering College, Ghaziabad. 21

You might also like

- Practical-1 AIM: Implement Register Transfer Operation in Logisim SimulatorDocument23 pagesPractical-1 AIM: Implement Register Transfer Operation in Logisim SimulatorDigvijay Sinh ChauhanNo ratings yet

- Sap 2Document35 pagesSap 2Michael Vincent B. Nierva88% (8)

- Tutorial Module 4Document9 pagesTutorial Module 4Neupane Er KrishnaNo ratings yet

- Lecture 12 - General Register OrganizationDocument6 pagesLecture 12 - General Register OrganizationPragya SinghNo ratings yet

- Seven Cpu RegistersDocument6 pagesSeven Cpu RegistersPriyanka PuvvalaNo ratings yet

- Unit1 Addressing Modes and GPRDocument70 pagesUnit1 Addressing Modes and GPRsaumya2213215No ratings yet

- Maes - Final - Lecture 04 - Fall 2023-24Document24 pagesMaes - Final - Lecture 04 - Fall 2023-24Kamal KhanNo ratings yet

- Register OrgaDocument15 pagesRegister OrgaKannan KannanNo ratings yet

- Ω Ω Ω. Find the β β β βDocument3 pagesΩ Ω Ω. Find the β β β βJoginder YadavNo ratings yet

- Module 3 - Part 1Document27 pagesModule 3 - Part 1barnabasNo ratings yet

- An Efficient 64-Bit Carry Select Adder With Less Delay and Reduced Area ApplicationDocument5 pagesAn Efficient 64-Bit Carry Select Adder With Less Delay and Reduced Area ApplicationkumaranrajNo ratings yet

- Microprocessor PDFDocument30 pagesMicroprocessor PDFAmy OliverNo ratings yet

- Design and Implementation of High Speed Carry Select AdderDocument6 pagesDesign and Implementation of High Speed Carry Select AdderseventhsensegroupNo ratings yet

- Unit 1 MPUOrganizationDocument90 pagesUnit 1 MPUOrganizationspam.me.adiNo ratings yet

- L-4rr-l/EEE Date: 25/09/2022Document50 pagesL-4rr-l/EEE Date: 25/09/2022Nure Alam DipuNo ratings yet

- Central Processing UnitDocument14 pagesCentral Processing UnitAditya KumarNo ratings yet

- Tutorial 3 2022 StudentsDocument5 pagesTutorial 3 2022 StudentsIndongo EliaserNo ratings yet

- Unit 1 Introduction To Processing UnitsDocument68 pagesUnit 1 Introduction To Processing UnitsAhan Tejaswi100% (1)

- Unit 1 Introduction To Processing UnitsDocument68 pagesUnit 1 Introduction To Processing Unitsapoorobot21No ratings yet

- Design and Performance Analysis of 8-Bit RISC Processor Using Xilinx & Microwind ToolDocument10 pagesDesign and Performance Analysis of 8-Bit RISC Processor Using Xilinx & Microwind ToolRakeshconclaveNo ratings yet

- F Capacitor, Find The Appropriate Value ofDocument2 pagesF Capacitor, Find The Appropriate Value ofJoginder YadavNo ratings yet

- CSA Test PaperDocument65 pagesCSA Test Paperhimanshumis2022No ratings yet

- Irjet V5i3295 PDFDocument3 pagesIrjet V5i3295 PDFchaitanya sNo ratings yet

- Notes Computer System Organization Unit 1Document11 pagesNotes Computer System Organization Unit 1Grace PatelNo ratings yet

- Lcdf3 Chap 10 p2Document32 pagesLcdf3 Chap 10 p2Ali Ahmad100% (1)

- General Purpose RegisterDocument7 pagesGeneral Purpose Registersaumya2213215No ratings yet

- MPMC 100 MCQ Set IDocument17 pagesMPMC 100 MCQ Set Ivlsimani9110No ratings yet

- Unit 1 MPU Organization PDFDocument96 pagesUnit 1 MPU Organization PDFSIDDHARTH TATHAGATNo ratings yet

- Files 3 Homework Solutions A5 Solution 081Document5 pagesFiles 3 Homework Solutions A5 Solution 081Ivanildo GomesNo ratings yet

- Implementation of AMBA APB Bridge With Efficient Deployment of System ResourcesDocument4 pagesImplementation of AMBA APB Bridge With Efficient Deployment of System Resourcesprojects allNo ratings yet

- Final ReportDocument24 pagesFinal Reportazmeeralal100% (2)

- Computer2 2Document19 pagesComputer2 2Priyanshu GuptaNo ratings yet

- Mimari ReportDocument27 pagesMimari ReportRomaan AliNo ratings yet

- WWW - Manaresults.co - In: Applications (Common To ECE, ETM)Document2 pagesWWW - Manaresults.co - In: Applications (Common To ECE, ETM)Syed AshmadNo ratings yet

- Position Control of An AC Servo Motor Using VHDL & Fpga: Kariyappa B. S., Hariprasad S. A., and R. NagarajDocument4 pagesPosition Control of An AC Servo Motor Using VHDL & Fpga: Kariyappa B. S., Hariprasad S. A., and R. NagarajBalu ViswanathNo ratings yet

- Design of Basic ComputerDocument29 pagesDesign of Basic ComputerM DEEPANANo ratings yet

- CS60003 High Performance Computer ArchitectureDocument3 pagesCS60003 High Performance Computer ArchitectureNarayan KunalNo ratings yet

- An Area Efficient Enhanced SQRT Carry Select Adder: Damarla Paradhasaradhi, Prof. K. AnusudhaDocument5 pagesAn Area Efficient Enhanced SQRT Carry Select Adder: Damarla Paradhasaradhi, Prof. K. AnusudhaSayyed Jaffar Ali RazaNo ratings yet

- Advanced RISC Machine-ARM Notes BhurchandiDocument8 pagesAdvanced RISC Machine-ARM Notes BhurchandiVipin TiwariNo ratings yet

- 15 - Chepter 6Document9 pages15 - Chepter 6vshalshethNo ratings yet

- A-Overview of EE3463: Intro To Micro's - Lab 1Document48 pagesA-Overview of EE3463: Intro To Micro's - Lab 1vikasNo ratings yet

- 4 - Bit - Carry - Propagate - Adder PDFDocument32 pages4 - Bit - Carry - Propagate - Adder PDFRennze Dominic DeveraNo ratings yet

- 8086 Instruction SetDocument113 pages8086 Instruction Setashok_ace01No ratings yet

- CA1 QB For Computer ArchitectureDocument4 pagesCA1 QB For Computer ArchitectureRajat SharmaNo ratings yet

- Csa 2022Document6 pagesCsa 2022Jha StockesNo ratings yet

- 134ak - Computer OrganizationDocument2 pages134ak - Computer Organizationsameeksha chiguruNo ratings yet

- PUE COA Solution 2022-23Document30 pagesPUE COA Solution 2022-23Aviral TaraNo ratings yet

- Be Winter 2022Document2 pagesBe Winter 2022Hiren PachaniNo ratings yet

- 4 Bit Cpu ReportDocument16 pages4 Bit Cpu ReportHarshil LodhiNo ratings yet

- Computer Applications and ManagementDocument11 pagesComputer Applications and ManagementParag PaliwalNo ratings yet

- Microcontroller - PDF 1411210674Document27 pagesMicrocontroller - PDF 1411210674Anney RevathiNo ratings yet

- Low Power and Area-Efficient Carry Select Adder: K.SaranyaDocument4 pagesLow Power and Area-Efficient Carry Select Adder: K.SaranyaUnita PailuNo ratings yet

- Data Transfer and Arithmetic InstructionsDocument6 pagesData Transfer and Arithmetic InstructionsAkshaya ThirumalairajNo ratings yet

- CA Assignment IIDocument9 pagesCA Assignment IISomesh ThakurNo ratings yet

- Semester Two Examinations - Summer 2007: Microprocessor Engineering 16-7210Document5 pagesSemester Two Examinations - Summer 2007: Microprocessor Engineering 16-7210amit panvekarNo ratings yet

- Ec6711 Embedded LaboratoryDocument56 pagesEc6711 Embedded LaboratorySeekay Alais Karuppaiah CNo ratings yet

- Chapter 1Document8 pagesChapter 1NIKHIL PUJARINo ratings yet

- First Internal Question Bank SUB: DSPA (10TE74) DATE: 03/09/2014Document2 pagesFirst Internal Question Bank SUB: DSPA (10TE74) DATE: 03/09/20149chand3No ratings yet

- Computer Architecture Unit 1Document35 pagesComputer Architecture Unit 1agamer43387No ratings yet

- Videocard Supported Upto 300mmDocument2 pagesVideocard Supported Upto 300mmArunkumar AKNo ratings yet

- AUTOSAR SWS CANInterfaceDocument212 pagesAUTOSAR SWS CANInterfaceAnuj SinghNo ratings yet

- Yocto SlidesDocument300 pagesYocto SlidesAbhinav ChoudharyNo ratings yet

- Siemens 023 FC2040 009384 B enDocument8 pagesSiemens 023 FC2040 009384 B enArman Ul NasarNo ratings yet

- Tracer - Universal Programmable Control Module - O&M ManualDocument272 pagesTracer - Universal Programmable Control Module - O&M ManualJonalou ArominNo ratings yet

- Oferta Cisco Echipamente Telecontrol Statie 110Document1 pageOferta Cisco Echipamente Telecontrol Statie 110Catalin DulceataNo ratings yet

- Database Installation Guide Microsoft WindowsDocument192 pagesDatabase Installation Guide Microsoft Windowsdinno riosNo ratings yet

- Computer GenerationsDocument10 pagesComputer GenerationsJimuel Libunao SupanNo ratings yet

- Assembly Language Programming - CS401 Power Point Slides Lecture 03Document24 pagesAssembly Language Programming - CS401 Power Point Slides Lecture 03usmanahmadawan100% (1)

- Servidor IBM3650M4Document62 pagesServidor IBM3650M4jose luisNo ratings yet

- IPASOLINK 400 MaintenanceDocument334 pagesIPASOLINK 400 Maintenancelegere100% (3)

- Draw #Item Description: With Ion. Cham. 5 Areas Normal VersionDocument41 pagesDraw #Item Description: With Ion. Cham. 5 Areas Normal VersionlegasuNo ratings yet

- Lecture 3 - Microprocessor Based SystemsDocument46 pagesLecture 3 - Microprocessor Based SystemsMuhammad AbdullahNo ratings yet

- What Is The Minimum Version of Oracle Linux Supported by The Oracle X8Document4 pagesWhat Is The Minimum Version of Oracle Linux Supported by The Oracle X8Khang DươngNo ratings yet

- SunUltra20USER819 2146 13Document134 pagesSunUltra20USER819 2146 13Félix EnríquezNo ratings yet

- Samsung 20 Pin Usb Data Cable and Headset Pinout Diagram GT-E1170 PhoneDocument3 pagesSamsung 20 Pin Usb Data Cable and Headset Pinout Diagram GT-E1170 PhoneduffsparkyNo ratings yet

- Guide 2: From Around Nov 2009: Edit: Don't Use This Guide Anymore!Document5 pagesGuide 2: From Around Nov 2009: Edit: Don't Use This Guide Anymore!Mierdadepollo DecagadaNo ratings yet

- ClaseDocument33 pagesClaseEva RomanNo ratings yet

- Coa M2020-026Document18 pagesCoa M2020-026Justine CastilloNo ratings yet

- Blue Screen After Sentinel Hardware Key Driver InstallationDocument2 pagesBlue Screen After Sentinel Hardware Key Driver InstallationThẩm Mỹ Hàn QuốcNo ratings yet

- MX512 ProdsheetDocument2 pagesMX512 ProdsheetXex AppealingNo ratings yet

- United States Patent 19 11 Patent Number: 5.453,933Document43 pagesUnited States Patent 19 11 Patent Number: 5.453,933Sandeep SNo ratings yet

- MsinfoDocument261 pagesMsinfoterraconstructionNo ratings yet

- CH 7b - Shift InstructionsDocument20 pagesCH 7b - Shift Instructionsapi-237335979100% (1)

- Internal HardwareDocument18 pagesInternal HardwareRojan Jay Climacosa100% (1)

- The Southbridge Is One of The Two Chips in The Core Logic Chipset On A Personal ComputerDocument9 pagesThe Southbridge Is One of The Two Chips in The Core Logic Chipset On A Personal ComputerMark Anthony PanahonNo ratings yet

- Intel Virtualization Technologies White PaperDocument6 pagesIntel Virtualization Technologies White PaperShrey FNo ratings yet

- 15.2 Practice Questions PDFDocument3 pages15.2 Practice Questions PDFKELLI MOSSNo ratings yet

- Input Data Into Computer: Parts of The ComputerDocument8 pagesInput Data Into Computer: Parts of The ComputerTricia Mae BatallaNo ratings yet